# INTRODUCTION TO OPERATING SYSTEMS

This text is disseminated via the Open Education Resource (OER) LibreTexts Project (https://LibreTexts.org) and like the hundreds of other texts available within this powerful platform, it is freely available for reading, printing and "consuming." Most, but not all, pages in the library have licenses that may allow individuals to make changes, save, and print this book. Carefully consult the applicable license(s) before pursuing such effects.

Instructors can adopt existing LibreTexts texts or Remix them to quickly build course-specific resources to meet the needs of their students. Unlike traditional textbooks, LibreTexts' web based origins allow powerful integration of advanced features and new technologies to support learning.

The LibreTexts mission is to unite students, faculty and scholars in a cooperative effort to develop an easy-to-use online platform for the construction, customization, and dissemination of OER content to reduce the burdens of unreasonable textbook costs to our students and society. The LibreTexts project is a multi-institutional collaborative venture to develop the next generation of open-access texts to improve postsecondary education at all levels of higher learning by developing an Open Access Resource environment. The project currently consists of 14 independently operating and interconnected libraries that are constantly being optimized by students, faculty, and outside experts to supplant conventional paper-based books. These free textbook alternatives are organized within a central environment that is both vertically (from advance to basic level) and horizontally (across different fields) integrated.

The LibreTexts libraries are Powered by NICE CXOne and are supported by the Department of Education Open Textbook Pilot Project, the UC Davis Office of the Provost, the UC Davis Library, the California State University Affordable Learning Solutions Program, and Merlot. This material is based upon work supported by the National Science Foundation under Grant No. 1246120, 1525057, and 1413739.

Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation nor the US Department of Education.

Have questions or comments? For information about adoptions or adaptions contact info@LibreTexts.org. More information on our activities can be found via Facebook (https://facebook.com/Libretexts), Twitter (https://twitter.com/libretexts), or our blog (http://Blog.Libretexts.org).

This text was compiled on 03/11/2025

# **TABLE OF CONTENTS**

## Licensing

# 1: Binary and Number Representation

- 1.1: How Computers See Numbers

- 1.2: Types and Number Representation

## 2: The Basics - An Overview

- 2.1: Introduction to Operating Systems

- o 2.2: Starting with the Basics

## 3: The Operating System

- o 3.1: The Role of the Operating System

- 3.2: Operating System Organisation

- o 3.3: System Calls

- o 3.4: Privileges

- 3.5: Function of the Operating System

- 3.6: Types of Operating Systems

- 3.6.1: Types of Operating Systems (continued)

- 3.6.2: Types of Operating Systems (continued)

- 3.7: Difference between multitasking, multithreading and multiprocessing

- 3.7.1: Difference between multitasking, multithreading and multiprocessing (continued)

- o 3.7.2: Difference between Multiprogramming, multitasking, multithreading and multiprocessing (continued)

# 4: Computer Architecture - the CPU

- 4.1: Instruction Cycles

- 4.1.1: Instruction Cycles Fetch

- 4.1.2: Instruction Cycles Instruction Primer

- 4.2: Interrupts

# 5: Computer Architecture - Memory

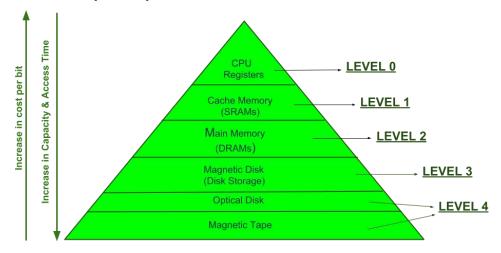

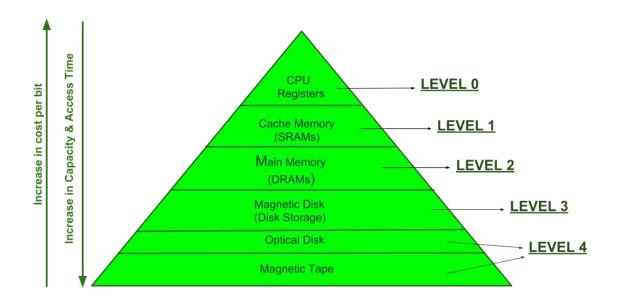

- 5.1: Memory Hierarchy

- 5.2: Memory Hierarchy (continued)

- 5.3: Cache Memory

- 5.3.1: Cache Memory Multilevel Cache

- 5.3.2: Cache Memory Locality of reference

- 5.4: Direct Memory Access

# 6: Computer Architecture - Peripherals and Buses

- o 6.1: Peripherals and buses

- 6.2: The Processor Bus

# 7: Small to Big Systems

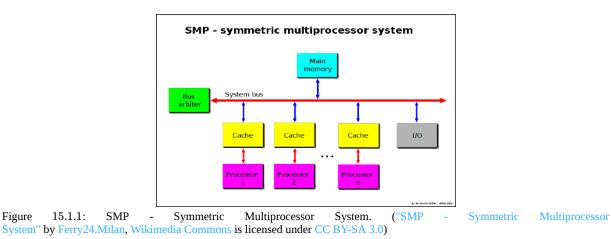

- 7.1: Symmetric Multi-Processing Systems

- 7.2: Multiprocessor and Multicore Systems

## 8: Processes

- 8.1: The Process

- 8.2: Processes

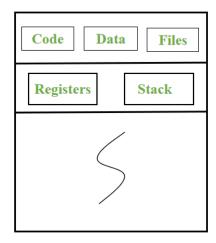

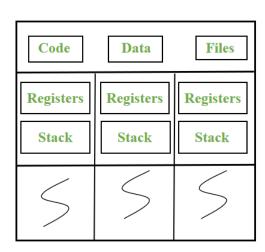

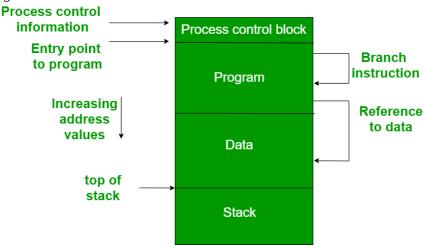

- 8.3: Elements of a process

- 8.4: Process States

- 8.5: Process Description

- 8.6: Process Control

- 8.7: Fork and Exec

- 8.8: Scheduling

- 8.9: Execution within the Operating System

- 8.9.1: Execution within the Operating System Dual Mode

- o 8.10: The Shell

- o 8.11: Signals

## 9: Threads

- o 9.1: Process and Threads

- 9.2: Thread Types

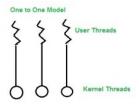

- 9.2.1: Thread Types Models

- 9.3: Thread Relationships

- o 9.4: Benefits of Multithreading

# 10: Concurrency and Process Synchronization

- 10.1: Introduction to Concurrency

- 10.2: Process Synchronization

- 10.3: Mutual Exclusion

- 10.4: Interprocess Communication

- 10.4.1: IPC Semaphores

- 10.4.2: IPC Monitors

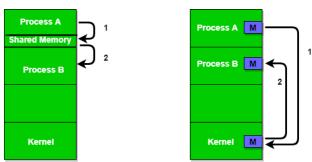

- 10.4.3: IPC Message Passing / Shared Memory

# 11: Concurrency- Deadlock and Starvation

- 11.1: Concept and Principles of Deadlock

- 11.2: Deadlock Detection and Prevention

- o 11.3: Starvation

- 11.4: Dining Philosopher Problem

# 12: Memory Management

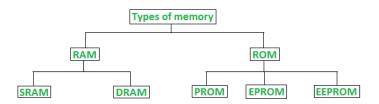

- 12.1: Random Access Memory (RAM) and Read Only Memory (ROM)

- 12.2: Memory Hierarchy

- 12.3: Requirements for Memory Management

- 12.4: Memory Partitioning

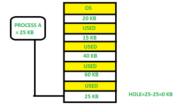

- 12.4.1: Fixed Partitioning

- 12.4.2: Variable Partitioning

- o 12.4.3: Buddy System

- 12.5: Logical vs Physical Address

- 12.6: Paging

- 12.7: Segmentation

# 13: Virtual Memory

- 13.1: Memory Paging

- 13.1.1: Memory Paging Page Replacement

- 13.2: Virtual Memory in the Operating System

# 14: Uniprocessor CPU Scheduling

- 14.1: Types of Processor Scheduling

- 14.2: Scheduling Algorithms

# 15: Multiprocessor Scheduling

- 15.1: The Question

- 15.2: Multiprocessor Scheduling

# 16: I/O and Disk Management

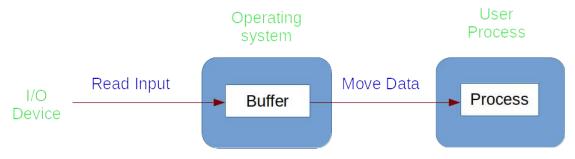

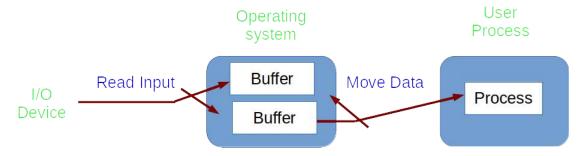

- 16.1: Input / Output

- 16.2: Types of I/O

- 16.3: I/O Buffering

- 16.4: Disk Drives in the OS

- 16.5: Disk Drive Scheduling

- o 16.6: RAID

# 17: File Management

- o 17.1: Overview

- o 17.2: Files

- o 17.2.1: Files (continued)

- 17.3: Directory

- 17.4: File Sharing

#### Index

## Glossary

## **Detailed Licensing**

# Licensing

A detailed breakdown of this resource's licensing can be found in **Back Matter/Detailed Licensing**.

# **CHAPTER OVERVIEW**

# 1: Binary and Number Representation

- 1.1: How Computers See Numbers

- 1.2: Types and Number Representation

<sup>1:</sup> Binary and Number Representation is shared under a not declared license and was authored, remixed, and/or curated by LibreTexts.

## 1.1: How Computers See Numbers

## Binary — the basis of computing

#### **Binary Theory**

#### Introduction

Binary is a base-2 number system that uses two mutually exclusive states to represent information. A binary number is made up of elements called *bits* where each bit can be in one of the two possible states. Generally, we represent them with the numerals and  $\circ$ . We also talk about them being true and false. Electrically, the two states might be represented by high and low voltages or some form of switch turned on or off.

We build binary numbers the same way we build numbers in our traditional base 10 system. However, instead of a one's column, a 10's column, a 100's column (and so on) we have a one's column, a two's columns, a four's column, an eight's column, and so on, as illustrated below.

Table 2.1. Binary

| 2 | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | $2^1$ | 2 <sup>0</sup> |

|---|----------------|----------------|----------------|----------------|----------------|-------|----------------|

|   | 64             | 32             | 16             | 8              | 4              | 2     | 1              |

For example, to represent the number 203 in base 10, we know we place a 3 in the 1's column, a 0 in the 10's column and a 2 in the 100's column. This is expressed with exponents in the table below.

Table 2.2. 203 in base 10

| 10 <sup>2</sup> | 10 <sup>1</sup> | 10 <sup>0</sup> |

|-----------------|-----------------|-----------------|

| 2               | 0               | 3               |

Or, in other words,  $2 \times 10^2 + 3 \times 10^0 = 200 + 3 = 203$ . To represent the same thing in binary, we would have the following table.

Table 2.3. 203 in base 2

| 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | $2^1$ | 2 <sup>0</sup> |

|----------------|----------------|----------------|----------------|----------------|----------------|-------|----------------|

| 1              | 1              | 0              | 0              | 1              | 0              | 1     | 1              |

That equates to  $2^7 + 2^6 + 2^3 + 2^1 + 2^0 = 128 + 64 + 8 + 2 + 1 = 203$ .

#### The basis of computing

You may be wondering how a simple number is the basis of all the amazing things a computer can do. Believe it or not, it is! The processor in your computer has a complex but ultimately limited set of *instructions* it can perform on values such as addition, multiplication, etc. Essentially, each of these instructions is assigned a number so that an entire program (add this to that, multiply by that, divide by this and so on) can be represented by a just a stream of numbers. For example, if the processor knows operation 2 is addition, then 252 could mean "add 5 and 2 and store the output somewhere". The reality is of course much more complicated (see Chapter 3, *Computer Architecture*) but, in a nutshell, this is what a computer is.

In the days of punch-cards, one could see with their eye the one's and zero's that make up the program stream by looking at the holes present on the card. Of course this moved to being stored via the polarity of small magnetic particles rather quickly (tapes, disks) and onto the point today that we can carry unimaginable amounts of data in our pocket.

Translating these numbers to something useful to humans is what makes a computer so useful. For example, screens are made up of millions of discrete *pixels*, each too small for the human eye to distinguish but combining to make a complete image. Generally each pixel has a certain red, green and blue component that makes up it's display color. Of course, these values can be represented by numbers, which of course can be represented by binary! Thus any image can be broken up into millions of individual dots, each dot represented by a *tuple* of three values representing the red, green and blue values for the pixel. Thus given a long string of such

numbers, formatted correctly, the video hardware in your computer can convert those numbers to electrical signals to turn on and off individual pixels and hence display an image.

As you read on, we will build up the entire modern computing environment from this basic building block; *from the bottom-up* if you will!

#### Bits and Bytes

As discussed above, we can essentially choose to represent anything by a number, which can be converted to binary and operated on by the computer. For example, to represent all the letters of the alphabet we would need at least enough different combinations to represent all the lower case letters, the upper case letters, numbers and punctuation, plus a few extras. Adding this up means we need probably around 80 different combinations.

If we have two bits, we can represent four possible unique combinations (  $00 \ 01 \ 10 \ 11$  ). If we have three bits, we can represent 8 different combinations. In general, with n bits we can represent  $2^n$  unique combinations.

8 bits gives us  $2^8 = 256$  unique representations, more than enough for our alphabet combinations. We call a group of 8 bits a *byte*. Guess how big a C char variable is? One byte.

#### **ASCII**

Given that a byte can represent any of the values 0 through 255, anyone could arbitrarily make up a mapping between characters and numbers. For example, a video card manufacturer could decide that 1 represents A, so when value 1 is sent to the video card it displays a capital 'A' on the screen. A printer manufacturer might decide for some obscure reason that 1 represented a lower-case 'z', meaning that complex conversions would be required to display and print the same thing.

To avoid this happening, the *American Standard Code for Information Interchange* or ASCII was invented. This is a *7-bit* code, meaning there are  $2^7$  or 128 available codes.

The range of codes is divided up into two major parts; the non-printable and the printable. Printable characters are things like characters (upper and lower case), numbers and punctuation. Non-printable codes are for control, and do things like make a carriage-return, ring the terminal bell or the special NULL code which represents nothing at all.

127 unique characters is sufficient for American English, but becomes very restrictive when one wants to represent characters common in other languages, especially Asian languages which can have many thousands of unique characters.

To alleviate this, modern systems are moving away from ASCII to *Unicode*, which can use up to 4 bytes to represent a character, giving *much* more room!

## Parity

ASCII, being only a 7-bit code, leaves one bit of the byte spare. This can be used to implement *parity* which is a simple form of error checking. Consider a computer using punch-cards for input, where a hole represents 1 and no hole represents 0. Any inadvertent covering of a hole will cause an incorrect value to be read, causing undefined behaviour.

Parity allows a simple check of the bits of a byte to ensure they were read correctly. We can implement either *odd* or *even* parity by using the extra bit as a *parity bit*.

In odd parity, if the number of 1's in the 7 bits of information is odd, the parity bit is set, otherwise it is not set. Even parity is the opposite; if the number of 1's is even the parity bit is set to 1.

In this way, the flipping of one bit will case a parity error, which can be detected.

XXX more about error correcting

#### 16, 32 and 64 bit computers

Numbers do not fit into bytes; hopefully your bank balance in dollars will need more range than can fit into one byte! Modern architectures are at least *32 bit* computers. This means they work with 4 bytes at a time when processing and reading or writing to memory. We refer to 4 bytes as a *word*; this is analogous to language where letters (bits) make up words in a sentence, except in computing every word has the same size! The size of a C int variable is 32 bits. Modern architectures are 64 bits, which doubles the size the processor works with to 8 bytes.

Kilo, Mega and Giga Bytes

Computers deal with a lot of bytes; that's what makes them so powerful! We need a way to talk about large numbers of bytes, and a natural way is to use the "International System of Units" (SI) prefixes as used in most other scientific areas. So for example, kilo refers to 10<sup>3</sup> or 1000 units, as in a kilogram has 1000 grams.

1000 is a nice round number in base 10, but in binary it is 1111101000 which is not a particularly "round" number. However, 1024 (or 2<sup>10</sup>) is a round number — ( 100000000000 — and happens to be quite close to the base 10 meaning value of "kilo" (1000 as opposed to 1024). Thus 1024 bytes naturally became known as a *kilobyte*. The next SI unit is "mega" for 10<sup>6</sup> and the prefixes continue upwards by 10<sup>3</sup> (corresponding to the usual grouping of three digits when writing large numbers). As it happens, 2<sup>20</sup> is again close to the SI base 10 definition for mega; 1048576 as opposed to 1000000. Increasing the base 2 units by powers of 10 remains functionally close to the SI base 10 value, although each increasing factor diverges slightly further from the base SI meaning. Thus the SI base-10 units are "close enough" and have become the commonly used for base 2 values.

Table 2.4. Base 2 and 10 factors related to bytes

| Name       | Base 2 Factor   | Bytes                     | Close Base 10 Factor | Base 10 bytes             |

|------------|-----------------|---------------------------|----------------------|---------------------------|

| 1 Kilobyte | 2 <sup>10</sup> | 1,024                     | 10 <sup>3</sup>      | 1,000                     |

| 1 Megabyte | 2 <sup>20</sup> | 1,048,576                 | 10 <sup>6</sup>      | 1,000,000                 |

| 1 Gigabyte | 2 <sup>30</sup> | 1,073,741,824             | 109                  | 1,000,000,000             |

| 1 Terabyte | 2 <sup>40</sup> | 1,099,511,627,776         | 10 <sup>12</sup>     | 1,000,000,000,000         |

| 1 Petabyte | 2 <sup>50</sup> | 1,125,899,906,842,624     | 10 <sup>15</sup>     | 1,000,000,000,000,000     |

| 1 Exabyte  | 2 <sup>60</sup> | 1,152,921,504,606,846,976 | 10 <sup>18</sup>     | 1,000,000,000,000,000,000 |

#### SI units compared in base 2 and base 10

It can be very useful to commit the base 2 factors to memory as an aid to quickly correlate the relationship between number-of-bits and "human" sizes. For example, we can quickly calculate that a 32 bit computer can address up to four gigabytes of memory by noting the recombination of  $2^2$  (4) +  $2^{30}$ . A 64-bit value could similarly address up to 16 exabytes ( $2^4 + 2^{60}$ ); you might be interested in working out just how big a number this is. To get a feel for how big that number is, calculate how long it would take to count to  $2^{64}$  if you incremented once per second.

#### Kilo, Mega and Giga Bits

Apart from the confusion related to the overloading of SI units between binary and base 10, capacities will often be quoted in terms of *bits* rather than bytes. Generally this happens when talking about networking or storage devices; you may have noticed that your ADSL connection is described as something like 1500 kilobits/second. The calculation is simple; multiply by 1000 (for the kilo), divide by 8 to get bytes and then 1024 to get kilobytes (so 1500 kilobits/s=183 kilobytes per second).

The SI standardisation body has recognised these dual uses and has specified unique prefixes for binary usage. Under the standard 1024 bytes is a kibibyte , short for *kilo binary* byte (shortened to KiB). The other prefixes have a similar prefix (Mebibyte, MiB, for example). Tradition largely prevents use of these terms, but you may seem them in some literature.

#### Conversion

The easiest way to convert between bases is to use a computer, after all, that's what they're good at! However, it is often useful to know how to do conversions by hand.

The easiest method to convert between bases is *repeated division*. To convert, repeatedly divide the quotient by the base, until the quotient is zero, making note of the remainders at each step. Then, write the remainders in reverse, starting at the bottom and appending to the right each time. An example should illustrate; since we are converting to binary we use a base of 2.

Table 2.5. Convert 203 to binary

| Quotient                |     | Remainder |   |

|-------------------------|-----|-----------|---|

| 203 <sub>10</sub> ÷ 2 = | 101 | 1         |   |

| 101 <sub>10</sub> ÷ 2 = | 50  | 1         | 1 |

| Quotient               |    | Remainder |          |

|------------------------|----|-----------|----------|

| 50 <sub>10</sub> ÷ 2 = | 25 | 0         | <b>↑</b> |

| 25 <sub>10</sub> ÷ 2 = | 12 | 1         | <b>↑</b> |

| 12 <sub>10</sub> ÷ 2 = | 6  | 0         | <b>↑</b> |

| 6 <sub>10</sub> ÷ 2 =  | 3  | 0         | <b>↑</b> |

| 3 <sub>10</sub> ÷ 2 =  | 1  | 1         | 1        |

| 1 <sub>10</sub> ÷ 2 =  | 0  | 1         | <b>↑</b> |

Reading from the bottom and appending to the right each time gives 11001011, which we saw from the previous example was 203.

#### **Boolean Operations**

George Boole was a mathematician who discovered a whole area of mathematics called *Boolean Algebra*. Whilst he made his discoveries in the mid 1800's, his mathematics are the fundamentals of all computer science. Boolean algebra is a wide ranging topic, we present here only the bare minimum to get you started.

Boolean operations simply take a particular input and produce a particular output following a rule. For example, the simplest boolean operation, not simply inverts the value of the input operand. Other operands usually take two inputs, and produce a single output.

The fundamental Boolean operations used in computer science are easy to remember and listed below. We represent them below with *truth tables*; they simply show all possible inputs and outputs. The term *true* simply reflects 1 in binary.

#### No:

Usually represented by  $\,!\,$  ,  $\,$  not  $\,$  simply inverts the value, so  $\,$  0  $\,$  becomes  $\,$  1  $\,$  and  $\,$  1  $\,$  becomes  $\,$  0

Table 2.6. Truth table for not

| Input | Output |

|-------|--------|

| 1     | 0      |

| 0     | 1      |

#### And

To remember how the and operation works think of it as "if one input and the other are true, result is true

Table 2.7. Truth table for and

| Input 1 | Input 2 | Output |

|---------|---------|--------|

| 0       | 0       | 0      |

| 1       | 0       | 0      |

| 0       | 1       | 0      |

| 1       | 1       | 1      |

#### Or

To remember how the or operation works think of it as "if one input *or* the other input is true, the result is true Table 2.8. Truth table for *or*

| Input 1 | Input 2 | Output |

|---------|---------|--------|

|---------|---------|--------|

| Input 1 | Input 2 | Output |

|---------|---------|--------|

| 0       | 0       | 0      |

| 1       | 0       | 1      |

| 0       | 1       | 1      |

| 1       | 1       | 1      |

#### Exclusive Or (xor)

Exclusive or, written as <code>xor</code> is a special case of <code>or</code> where the output is true if one, and *only* one, of the inputs is true. This operation can surprisingly do many interesting tricks, but you will not see a lot of it in the kernel.

Table 2.9. Truth table for *xor*

| Input 1 | Input 2 | Output |

|---------|---------|--------|

| 0       | 0       | 0      |

| 1       | 0       | 1      |

| 0       | 1       | 1      |

| 1       | 1       | 0      |

#### How computers use boolean operations

Believe it or not, essentially everything your computer does comes back to the above operations. For example, the half adder is a type of circuit made up from boolean operations that can add bits together (it is called a half adder because it does not handle carry bits). Put more half adders together, and you will start to build something that can add together long binary numbers. Add some external memory, and you have a computer.

Electronically, the boolean operations are implemented in *gates* made by *transistors*. This is why you might have heard about transistor counts and things like Moore's Law. The more transistors, the more gates, the more things you can add together. To create the modern computer, there are an awful lot of gates, and an awful lot of transistors. Some of the latest Itanium processors have around 460 million transistors.

#### Working with binary in C

In C we have a direct interface to all of the above operations. The following table describes the operators

Table 2.10. Boolean operations in C

| Operation | Usage in C |

|-----------|------------|

| not       | !          |

| and       | &          |

| or        |            |

| xor       | ^          |

We use these operations on variables to modify the bits within the variable. Before we see examples of this, first we must divert to describe hexadecimal notation.

#### Hexadecimal

Hexadecimal refers to a base 16 number system. We use this in computer science for only one reason, it makes it easy for humans to think about binary numbers. Computers only ever deal in binary and hexadecimal is simply a shortcut for us humans trying to work with the computer.

So why base 16? Well, the most natural choice is base 10, since we are used to thinking in base 10 from our every day number system. But base 10 does not work well with binary -- to represent 10 different elements in binary, we need four bits. Four bits, however, gives us sixteen possible combinations. So we can either take the very tricky road of trying to convert between base 10 and binary, or take the easy road and make up a base 16 number system -- hexadecimal!

Hexadecimal uses the standard base 10 numerals, but adds A B C D E F which refer to 10 11 12 13 14 15 (n.b. we start from zero).

Traditionally, any time you see a number prefixed by  $\Theta \times$  this will denote a hexadecimal number.

As mentioned, to represent 16 different patterns in binary, we would need exactly four bits. Therefore, each hexadecimal numeral represents exactly four bits. You should consider it an exercise to learn the following table off by heart.

Table 2.11. Hexadecimal, Binary and Decimal

| Hexadecimal | Binary | Decimal |

|-------------|--------|---------|

| 0           | 0000   | 0       |

| 1           | 0001   | 1       |

| 2           | 0010   | 2       |

| 3           | 0011   | 3       |

| 4           | 0100   | 4       |

| 5           | 0101   | 5       |

| 6           | 0110   | 6       |

| 7           | 0111   | 7       |

| 8           | 1000   | 8       |

| 9           | 1001   | 9       |

| А           | 1010   | 10      |

| В           | 1011   | 11      |

| С           | 1100   | 12      |

| D           | 1101   | 13      |

| Е           | 1110   | 14      |

| F           | 1111   | 15      |

Of course there is no reason not to continue the pattern (say, assign G to the value 16), but 16 values is an excellent trade off between the vagaries of human memory and the number of bits used by a computer (occasionally you will also see base 8 used, for example for file permissions under UNIX). We simply represent larger numbers of bits with more numerals. For example, a sixteen bit variable can be represented by 0xAB12, and to find it in binary simply take each individual numeral, convert it as per the table and join them all together (so 0xAB12 ends up as the 16-bit binary number 1010101100010010). We can use the reverse to convert from binary back to hexadecimal.

We can also use the same repeated division scheme to change the base of a number. For example, to find 203 in hexadecimal

Table 2.12. Convert 203 to hexadecimal

| Quotient                 |    | Remainder |  |

|--------------------------|----|-----------|--|

| 203 <sub>10</sub> ÷ 16 = | 12 | 11 (0xB)  |  |

| Quotient                |   | Remainder |          |

|-------------------------|---|-----------|----------|

| 12 <sub>10</sub> ÷ 16 = | 0 | 12 (0xC)  | <b>↑</b> |

Hence 203 in hexadecimal is 0xCB.

#### **Practical Implications**

#### Use of binary in code

Whilst binary is the underlying language of every computer, it is entirely practical to program a computer in high level languages without knowing the first thing about it. However, for the low level code we are interested in a few fundamental binary principles are used repeatedly.

#### Masking and Flags

#### Masking

In low level code, it is often important to keep your structures and variables as space efficient as possible. In some cases, this can involve effectively packing two (generally related) variables into one.

Remember each bit represents two states, so if we know a variable only has, say, 16 possible states it can be represented by 4 bits (i.e.  $2^4$ =16 unique values). But the smallest type we can declare in C is 8 bits (a char), so we can either waste four bits, or find some way to use those left over bits.

We can easily do this by the process of *masking*. This uses the rules of logical operations to extract values.

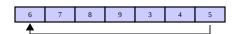

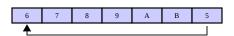

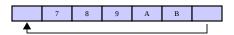

The process is illustrated in the figure below. We can keep two separate 4-bit values "inside" a single 8-bit character. We consider the upper four-bits as one value (blue) and the lower 4-bits (red) as another. To extract the lower four bits, we set our mask to have the lower-4 bits set to 1 ( $0\times0F$ ). Since the logical and operation will only set the bit if both bits are 1, those bits of the mask set to 0 effectively hide the bits we are not interested in.

Figure 2.1. Masking

To get the top (blue) four bits, we would invert the mask; in other words, set the top 4 bits to 1 and the lower 4-bits to 0. You will note this gives a result of 1010 0000 (or, in hexadecimal  $0\times A0$ ) when really we want to consider this as a unique 4-bit value 1010 ( $0\times 0A$ ). To get the bits into the right position we use the right shift operation 4 times, giving a final value of 0000 1010.

Example 2.1. Using masks

1 #include <stdio.h>

#define LOWER\_MASK 0x0F

#define UPPER\_MASK 0xF0

5

int main(int argc, char\* argv[])

{

/\* Two 4-bit values stored in one

\* 8-bit variable \*/

10 char value = 0xA5;

```

char lower = value & LOWER_MASK;

char upper = (value & UPPER_MASK) >> 4;

printf("Lower: %x\n", lower);

printf("Upper: %x\n", upper);

}

```

*Setting* the bits requires the logical or operation. However, rather than using 1 's as the mask, we use 0 's. You should draw a diagram similar to the above figure and work through setting bits with the logical or operation.

#### Flags

Often a program will have a large number of variables that only exist as *flags* to some condition. For example, a state machine is an algorithm that transitions through a number of different states but may only be in one at a time. Say it has 8 different states; we could easily declare 8 different variables, one for each state. But in many cases it is better to declare *one* 8 bit variable and assign each bit to *flag* flag a particular state.

Flags are a special case of masking, but each bit represents a particular boolean state (on or off). An n bit variable can hold n different flags. See the code example below for a typical example of using flags -- you will see variations on this basic code very often.

```

Example 2.2. Using flags

1 #include <stdio.h>

define all 8 possible flags for an 8 bit variable

name hex

binary

#define FLAG1 0x01 /* 00000001 */

#define FLAG2 0x02 /* 00000010 */

#define FLAG3 0x04 /* 00000100 */

10 #define FLAG4 0x08 /* 00001000 */

/* ... and so on */

#define FLAG8 0x80 /* 10000000 */

int main(int argc, char *argv[])

15 {

char flags = 0; /* an 8 bit variable */

/* set flags with a logical or */

flags = flags | FLAG1; /* set flag 1 */

20

flags = flags | FLAG3; /* set flag 3

/* check flags with a logical and. If the flag is set (1)

* then the logical and will return 1, causing the if

* condition to be true. */

25

if (flags & FLAG1)

printf("FLAG1 set!\n");

```

This page titled 1.1: How Computers See Numbers is shared under a CC BY-SA 4.0 license and was authored, remixed, and/or curated by Patrick McClanahan.

## 1.2: Types and Number Representation

## Types and Number Representation

#### C Standards

Although a slight divergence, it is important to understand a bit of history about the C language.

C is the common language of the systems programming world. Every operating system and its associated system libraries in common use is written in C, and every system provides a C compiler. To stop the language diverging across each of these systems where each would be sure to make numerous incompatible changes, a strict standard has been written for the language.

Officially this standard is known as ISO/IEC 9899:1999(E), but is more commonly referred to by its shortened name *C99*. The standard is maintained by the International Standards Organisation (ISO) and the full standard is available for purchase online. Older standards versions such as C89 (the predecessor to C99 released in 1989) and ANSI C are no longer in common usage and are encompassed within the latest standard. The standard documentation is very technical, and details most every part of the language. For example it explains the syntax (in Backus Naur form), standard #define values and how operations should behave.

It is also important to note what the C standards does *not* define. Most importantly the standard needs to be appropriate for every architecture, both present and future. Consequently it takes care *not* to define areas that are architecture dependent. The "glue" between the C standard and the underlying architecture is the Application Binary Interface (or ABI) which we discuss below. In several places the standard will mention that a particular operation or construct has an unspecified or implementation dependent result. Obviously the programmer can not depend on these outcomes if they are to write portable code.

#### **GNU C**

The GNU C Compiler, more commonly referred to as gcc, almost completely implements the C99 standard. However it also implements a range of extensions to the standard which programmers will often use to gain extra functionality, at the expense of portability to another compiler. These extensions are usually related to very low level code and are much more common in the system programming field; the most common extension being used in this area being inline assembly code. Programmers should read the gcc documentation and understand when they may be using features that diverge from the standard.

gcc can be directed to adhere strictly to the standard (the -std=c99 flag for example) and warn or create an error when certain things are done that are not in the standard. This is obviously appropriate if you need to ensure that you can move your code easily to another compiler.

#### **Types**

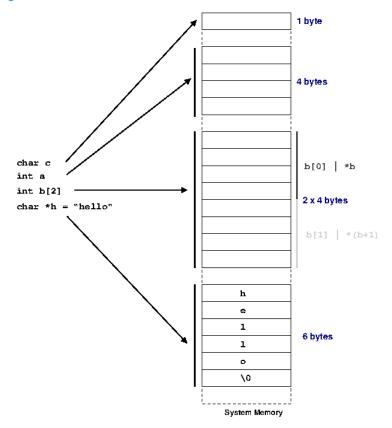

As programmers, we are familiar with using variables to represent an area of memory to hold a value. In a *typed* language, such as C, every variable must be declared with a *type*. The type tells the compiler about what we expect to store in a variable; the compiler can then both allocate sufficient space for this usage and check that the programmer does not violate the rules of the type. In the example below, we see an example of the space allocated for some common types of variables.

Figure 2.2. Types

The C99 standard purposely only mentions the *smallest* possible size of each of the types defined for C. This is because across different processor architectures and operating systems the best size for types can be wildly different.

To be completely safe programmers need to never assume the size of any of their variables, however a functioning system obviously needs agreements on what sizes types are going to be used in the system. Each architecture and operating system conforms to an *Application Binary Interface* or *ABI*. The ABI for a system fills in the details between the C standard and the requirements of the underlying hardware and operating system. An ABI is written for a specific processor and operating system combination.

Table 2.13. Standard Integer Types and Sizes

| Туре      | C99 minimum size (bits)  | Common size (32 bit architecture) |

|-----------|--------------------------|-----------------------------------|

| char      | 8                        | 8                                 |

| short     | 16                       | 16                                |

| int       | 16                       | 32                                |

| long      | 32                       | 32                                |

| long long | 64                       | 64                                |

| Pointers  | Implementation dependent | 32                                |

Above we can see the only divergence from the standard is that <code>int</code> is commonly a 32 bit quantity, which is twice the strict minimum 16 bit size that the C99 requires.

Pointers are really just an address (i.e. their value is an address and thus "points" somewhere else in memory) therefore a pointer needs to be sufficient in size to be able to address any memory in the system.

#### 64 hit

One area that causes confusion is the introduction of 64 bit computing. This means that the processor can handle addresses 64 bits in length (specifically the registers are 64 bits wide; a topic we discuss in Chapter 3, Computer Architecture).

This firstly means that all pointers are required to be a 64 bits wide so they can represent any possible address in the system. However, system implementers must then make decisions about the size of the other types. Two common models are widely used, as shown below.

Table 2.14. Standard Scalar Types and Sizes

| Туре      | C99 minimum size (bits)  | Common size (LP64) | Common size (Windows) |

|-----------|--------------------------|--------------------|-----------------------|

| char      | 8                        | 8                  | 8                     |

| short     | 16                       | 16                 | 16                    |

| int       | 16                       | 32                 | 32                    |

| long      | 32                       | 64                 | 32                    |

| long long | 64                       | 64                 | 64                    |

| Pointers  | Implementation dependent | 64                 | 64                    |

You can see that in the LP64 (long-pointer 64) model long values are defined to be 64 bits wide. This is different to the 32 bit model we showed previously. The LP64 model is widely used on UNIX systems.

In the other model, long remains a 32 bit value. This maintains maximum compatibility with 32 code. This model is in use with 64 bit Windows.

There are good reasons why the size of int was not increased to 64 bits in either model. Consider that if the size of int is increased to 64 bits you leave programmers no way to obtain a 32 bit variable. The only possibly is redefining shorts to be a larger 32 bit type.

A 64 bit variable is so large that it is not generally required to represent many variables. For example, loops very rarely repeat more times than would fit in a 32 bit variable (4294967296 times!). Images usually are usually represented with 8 bits for each of a red, green and blue value and an extra 8 bits for extra (alpha channel) information; a total of 32 bits. Consequently for many cases, using a 64 bit variable will be wasting at least the top 32 bits (if not more). Not only this, but the size of an integer array has now doubled too. This means programs take up more system memory (and thus more cache; discussed in detail in Chapter 3, Computer Architecture) for no real improvement. For the same reason Windows elected to keep their long values as 32 bits; since much of the Windows API was originally written to use long variables on a 32 bit system and hence does not require the extra bits this saves considerable wasted space in the system without having to re-write all the API.

If we consider the proposed alternative where short was redefined to be a 32 bit variable; programmers working on a 64 bit system could use it for variables they know are bounded to smaller values. However, when moving back to a 32 bit system their same short variable would now be only 16 bits long, a value which is much more realistically overflowed (65536).

By making a programmer request larger variables when they know they will be needed strikes a balance with respect to portability concerns and wasting space in binaries.

#### Type qualifiers

The C standard also talks about some qualifiers for variable types. For example <code>const</code> means that a variable will never be modified from its original value and <code>volatile</code> suggests to the compiler that this value might change outside program execution flow so the compiler must be careful not to re-order access to it in any way.

signed and unsigned are probably the two most important qualifiers; and they say if a variable can take on a negative value or not. We examine this in more detail below.

Qualifiers are all intended to pass extra information about how the variable will be used to the compiler. This means two things; the compiler can check if you are violating your own rules (e.g. writing to a const value) and it can make optimisations based upon the extra knowledge (examined in later chapters).

#### Standard Types

C99 realises that all these rules, sizes and portability concerns can become very confusing very quickly. To help, it provides a series of special types which can specify the exact properties of a variable. These are defined in <stdint.h> and have the form qtypes\_t where q is a qualifier, type is the base type, s is the width in bits and \_t is an extension so you know you are using the C99 defined types.

So for example uint8\_t is an unsigned integer exactly 8 bits wide. Many other types are defined; the complete list is detailed in C99 17.8 or (more cryptically) in the header file. [3]

It is up to the system implementing the C99 standard to provide these types for you by mapping them to appropriate sized types on the target system; on Linux these headers are provided by the system libraries.

#### Types in action

Below in Example 2.3, "Example of warnings when types are not matched" we see an example of how types place restrictions on what operations are valid for a variable, and how the compiler can use this information to warn when variables are used in an incorrect fashion. In this code, we firstly assign an integer value into a char variable. Since the char variable is smaller, we loose the correct value of the integer. Further down, we attempt to assign a pointer to a char to memory we designated as an integer. This operation can be done; but it is not safe. The first example is run on a 32-bit Pentium machine, and the correct value is returned. However, as shown in the second example, on a 64-bit Itanium machine a pointer is 64 bits (8 bytes) long, but an integer is only 4 bytes long. Clearly, 8 bytes can not fit into 4! We can attempt to "fool" the compiler by *casting* the value before assigning it; note that in this case we have shot ourselves in the foot by doing this cast and ignoring the compiler warning since the smaller variable can not hold all the information from the pointer and we end up with an invalid address.

Example 2.3. Example of warnings when types are not matched

```

* types.c

5 #include <stdio.h>

#include <stdint.h>

int main(void)

{

10

char a;

char *p = "hello";

int i;

15

// moving a larger variable into a smaller one

i = 0 \times 12341234;

a = i;

i = a;

printf("i is %d\n", i);

20

// moving a pointer into an integer

printf("p is %p \n", p);

i = p;

// "fooling" with casts

25

i = (int)p;

p = (char^*)i;

```

```

printf("p is %p\n", p);

return 0;

30 }

```

```

1 $ uname -m

i686

$ gcc -Wall -o types types.c

5 types.c: In function 'main':

types.c:19: warning: assignment makes integer from pointer without a cast

$ ./types

i is 52

10 p is 0x80484e8

p is 0x80484e8

$ uname -m

ia64

15

$ gcc -Wall -o types types.c

types.c: In function 'main':

types.c:19: warning: assignment makes integer from pointer without a cast

types.c:21: warning: cast from pointer to integer of different size

20 types.c:22: warning: cast to pointer from integer of different size

$ ./types

i is 52

p is 0x400000000000009e0

25 p is 0x9e0

```

#### **Number Representation**

#### **Negative Values**

With our modern base 10 numeral system we indicate a negative number by placing a minus ( - ) sign in front of it. When using binary we need to use a different system to indicate negative numbers.

There is only one scheme in common use on modern hardware, but C99 defines three acceptable methods for negative value representation.

#### Sign Bit

The most straight forward method is to simply say that one bit of the number indicates either a negative or positive value depending on it being set or not.

This is analogous to mathematical approach of having a  $\,^+\,$  and  $\,^-\,$ . This is fairly logical, and some of the original computers did represent negative numbers in this way. But using binary numbers opens up some other possibilities which make the life of hardware designers easier.

However, notice that the value  $\Theta$  now has two equivalent values; one with the sign bit set and one without. Sometimes these values are referred to as  $+\Theta$  and  $-\Theta$  respectively.

#### One's Complement

One's complement simply applies the *not* operation to the positive number to represent the negative number. So, for example the value -90 (-0x5A) is represented by  $\sim 0.1011010 = 10100101$  [4]

With this scheme the biggest advantage is that to add a negative number to a positive number no special logic is required, except that any additional carry left over must be added back to the final value. Consider

Table 2.15. One's Complement Addition

| Decimal | Binary                | Op |

|---------|-----------------------|----|

| -90     | 10100101              | +  |

| 100     | 01100100              |    |

|         |                       |    |

| 10      | <sup>1</sup> 00001001 | 9  |

|         | 00001010              | 10 |

If you add the bits one by one, you find you end up with a carry bit at the end (highlighted above). By adding this back to the original we end up with the correct value, 10

Again we still have the problem with two zeros being represented. Again no modern computer uses one's complement, mostly because there is a better scheme.

#### Two's Complement

Two's complement is just like one's complement, except the negative representation has *one* added to it and we discard any left over carry bit. So to continue with the example from before, -90 would be -01011010+1=10100101+1=10100101+1=101001101.

This means there is a slightly odd symmetry in the numbers that can be represented; for example with an 8 bit integer we have  $2^{8} = 256$  possible values; with our sign bit representation we could represent -127 thru 127 but with two's complement we can represent -127 thru 128. This is because we have removed the problem of having two zeros; consider that "negative zero" is (-000000000 +1)=(11111111+1)=000000000 (note discarded carry bit).

Table 2.16. Two's Complement Addition

| Decimal | Binary   | Op |

|---------|----------|----|

| -90     | 10100110 | +  |

| 100     | 01100100 |    |

|         |          |    |

| 10      | 00001010 |    |

You can see that by implementing two's complement hardware designers need only provide logic for addition circuits; subtraction can be done by two's complement negating the value to be subtracted and then adding the new value.

Similarly you could implement multiplication with repeated addition and division with repeated subtraction. Consequently two's complement can reduce all simple mathematical operations down to addition!

All modern computers use two's complement representation.

#### Sign-extension

Because of two's complement format, when increasing the size of signed value, it is important that the additional bits be *sign-extended*; that is, copied from the top-bit of the existing value.

Thanks to two's complement, it is sufficient to take the top bit of the exiting value and replace all the added bits with this value. This processes is referred to as *sign-extension* and is usually handled by the compiler in situations as defined by the language standard, with the processor generally providing special instructions to take a value and sign-extended it to some larger value.

#### Floating Point

So far we have only discussed integer or whole numbers; the class of numbers that can represent decimal values is called *floating point*.

To create a decimal number, we require some way to represent the concept of the decimal place in binary. The most common scheme for this is known as the *IEEE-754 floating point standard* because the standard is published by the Institute of Electric and Electronics Engineers. The scheme is conceptually quite simple and is somewhat analogous to "scientific notation".

In scientific notation the value 123.45 might commonly be represented as  $1.2345 \times 10^2$ . We call 1.2345 the *mantissa* or *significand*, 10 is the *radix* and 2 is the *exponent*.

In the IEEE floating point model, we break up the available bits to represent the sign, mantissa and exponent of a decimal number. A decimal number is represented by  $sign \times significand \times 2^{nexponent}$ .

The sign bit equates to either 1 or -1. Since we are working in binary, we always have the implied radix of 2.

There are differing widths for a floating point value -- we examine below at only a 32 bit value. More bits allows greater precision.

Table 2.17. IEEE Floating Point

| Sign | Exponent | Significand/Mantissa                    |

|------|----------|-----------------------------------------|

| S    | EEEEEEEE | MMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMMM |

The other important factor is *bias* of the exponent. The exponent needs to be able to represent both positive and negative values, thus an implied value of 127 is subtracted from the exponent. For example, an exponent of 0 has an exponent field of 127, 128 would represent 1 and 126 would represent -1.

Each bit of the significand adds a little more precision to the values we can represent. Consider the scientific notation representation of the value 198765. We could write this as  $1.98765 \times 10^6$ , which corresponds to a representation below

Table 2.18. Scientific Notation for 1.98765x10^6

| 10 <sup>0</sup> | • | 10-1 | 10-2 | 10-3 | 10-4 | 10-5 |

|-----------------|---|------|------|------|------|------|

| 1               | • | 9    | 8    | 7    | 6    | 5    |

Each additional digit allows a greater range of decimal values we can represent. In base 10, each digit after the decimal place increases the precision of our number by 10 times. For example, we can represent 0.0 through 0.9 (10 values) with one digit of decimal place, 0.00 through 0.99 (100 values) with two digits, and so on. In binary, rather than each additional digit giving us 10 times the precision, we only get two times the precision, as illustrated in the table below. This means that our binary representation does not always map in a straight-forward manner to a decimal representation.

Table 2.19. Significands in binary

| 2 <sup>0</sup> | • | 2-1 | 2-2  | 2-3   | 2 <sup>-4</sup> | 2 <sup>-5</sup> |

|----------------|---|-----|------|-------|-----------------|-----------------|

| 1              |   | 1/2 | 1/4  | 1/8   | 1/16            | 1/32            |

| 1              |   | 0.5 | 0.25 | 0.125 | 0.0625          | 0.03125         |

With only one bit of precision, our fractional precision is not very big; we can only say that the fraction is either 0 or 0.5. If we add another bit of precision, we can now say that the decimal value is one of either 0, 0.25, 0.5, 0.75. With another bit of precision we can now represent the values 0, 0.125, 0.25, 0.375, 0.5, 0.625, 0.75, 0.875.

Increasing the number of bits therefore allows us greater and greater precision. However, since the range of possible numbers is infinite we will never have enough bits to represent *any* possible value.

For example, if we only have two bits of precision and need to represent the value 0.3 we can only say that it is closest to 0.25; obviously this is insufficient for most any application. With 22 bits of significand we have a much finer resolution, but it is still not enough for most applications. A double value increases the number of significand bits to 52 (it also increases the range of exponent values too). Some hardware has an 84-bit float, with a full 64 bits of significand. 64 bits allows a tremendous precision and should be suitable for all but the most demanding of applications (XXX is this sufficient to represent a length to less than the size of an atom?)

Example 2.4. Floats versus Doubles

```

1 $ cat float.c

#include <stdio.h>

int main(void)

5 {

float a = 0.45;

float b = 8.0;

double ad = 0.45;

double bd = 8.0;

10

printf("float+float, 6dp : %f\n", a+b);

printf("double+double, 6dp : %f\n", ad+bd);

printf("float+float, 20dp : %10.20f\n", a+b);

printf("dobule+double, 20dp : %10.20f\n", ad+bd);

15

return 0;

}

20 $ gcc -o float float.c

$ ./float

float+float, 6dp

: 8.450000

double+double, 6dp : 8.450000

25 float+float, 20dp : 8.44999998807907104492

dobule+double, 20dp : 8.4499999999999928946

$ python

Python 2.4.4 (#2, Oct 20 2006, 00:23:25)

30 [GCC 4.1.2 20061015 (prerelease) (Debian 4.1.1-16.1)] on linux2

Type "help", "copyright", "credits" or "license" for more information.

>>> 8.0 + 0.45

8.449999999999993

35

```

A practical example is illustrated above. Notice that for the default 6 decimal places of precision given by printf both answers are the same, since they are rounded up correctly. However, when asked to give the results to a larger precision, in this case 20 decimal places, we can see the results start to diverge. The code using doubles has a more accurate result, but it is still not exactly correct. We can also see that programmers not explicitly dealing with float values still have problems with precision of variables!

#### Normalised Values

scientific we can represent value in many different For example. a wavs.  $10023 \times 10^{10} = 1002.3 \times 10^{1} = 100.23 \times 10^{2}$ . We thus define the *normalised* version as where the 1/radix <= significand < 1 . In binary this ensures that the leftmost bit of the significand is always one. Knowing this, we can gain an extra bit of precision by having the standard say that the leftmost bit being one is implied.

Table 2.20. Example of normalising 0.375

| 2 <sup>0</sup> | 2-1 | 2-2 | 2 <sup>-3</sup> | 2-4 | 2 <sup>-5</sup> | Exponent         | Calculation              |

|----------------|-----|-----|-----------------|-----|-----------------|------------------|--------------------------|

| 0              | 0   | 1   | 1               | 0   | 0               | 2^ <sup>0</sup>  | (0.25+0.125) × 1 = 0.375 |

| 0              | 1   | 1   | 0               | 0   | 0               | 2^-1             | (0.5+0.25)×.5=0.375      |

| 1              | 1   | 0   | 0               | 0   | 0               | 2^ <sup>-2</sup> | (1+0.5)×0.25=0.375       |

As you can see above, we can make the value normalised by moving the bits upwards as long as we compensate by increasing the exponent.

#### **Normalisation Tricks**

A common problem programmers face is finding the first set bit in a bitfield. Consider the bitfield 0100; from the right the first set bit would be bit 2 (starting from zero, as is conventional).

The standard way to find this value is to shift right, check if the uppermost bit is a 1 and either terminate or repeat. This is a slow process; if the bitfield is 64 bits long and only the very last bit is set, you must go through all the preceding 63 bits!

However, if this bitfield value were the signficand of a floating point number and we were to normalise it, the value of the exponent would tell us how many times it was shifted. The process of normalising a number is generally built into the floating point hardware unit on the processor, so operates very fast; usually much faster than the repeated shift and check operations.

The example program below illustrates two methods of finding the first set bit on an Itanium processor. The Itanium, like most server processors, has support for an 80-bit *extended* floating point type, with a 64-bit significand. This means a unsigned long neatly fits into the significand of a long double. When the value is loaded it is normalised, and and thus by reading the exponent value (minus the 16 bit bias) we can see how far it was shifted.

Example 2.5. Program to find first set bit

```

15  // this value is normalised when it is loaded

long double d = 0x8000UL;

long exp;

// Itanium "get floating point exponent" instruction

20    asm ("getf.exp %0=%1" : "=r"(exp) : "f"(d));

// note exponent include bias

printf("The first non-zero (fast) is %d\n", exp - 65535);

25 }

```

#### Bringing it together

In the example code below we extract the components of a floating point number and print out the value it represents. This will only work for a 32 bit floating point value in the IEEE format; however this is common for most architectures with the float type.

```

Example 2.6. Examining Floats

1 #include <stdio.h>

#include <string.h>

#include <stdlib.h>

5 /* return 2^n */

int two_to_pos(int n)

{

if (n == 0)

return 1;

return 2 * two_to_pos(n - 1);

10

}

double two_to_neg(int n)

15

if (n == 0)

return 1;

return 1.0 / (two_to_pos(abs(n)));

}

20 double two_to(int n)

{

if (n \ge 0)

return two_to_pos(n);

if (n < 0)

25

return two_to_neg(n);

return 0;

```

```

/* Go through some memory "m" which is the 24 bit significand of a

floating point number. We work "backwards" from the bits

30

furthest on the right, for no particular reason. */

double calc_float(int m, int bit)

/* 23 bits; this terminates recursion */

35

if (bit > 23)

return 0;

/* if the bit is set, it represents the value 1/2^bit */

if ((m >> bit) & 1)

40

return 1.0L/two_to(23 - bit) + calc_float(m, bit + 1);

/* otherwise go to the next bit */

return calc_float(m, bit + 1);

}

45

int main(int argc, char *argv[])

float f;

int m,i,sign,exponent,significand;

50

if (argc != 2)

{

printf("usage: float 123.456\n");

exit(1);

55

}

if (sscanf(argv[1], "%f", &f) != 1)

{

printf("invalid input\n");

60

exit(1);

}

/* We need to "fool" the compiler, as if we start to use casts

(e.g. (int)f) it will actually do a conversion for us. We

65

want access to the raw bits, so we just copy it into a same

sized variable. */

memcpy(&m, &f, 4);

/* The sign bit is the first bit */

70

sign = (m >> 31) \& 0x1;

/* Exponent is 8 bits following the sign bit */

exponent = ((m >> 23) \& 0xFF) - 127;

```

```

/* Significand fills out the float, the first bit is implied

75

to be 1, hence the 24 bit OR value below. */

significand = (m \& 0x7FFFFF) | 0x800000;

/* print out a power representation */

printf("%f = %d * (", f, sign ? -1 : 1);

80

for(i = 23 ; i >= 0 ; i--)

if ((significand >> i) & 1)

printf("%s1/2^%d", (i == 23) ? "" : " + ",

85

printf(") * 2^%d\n", exponent);

/* print out a fractional representation */

printf("%f = %d * (", f, sign ? -1 : 1);

90

for(i = 23 ; i >= 0 ; i--)

if ((significand >> i) & 1)

printf("%s1/%d", (i == 23) ? "" : " + ",

95

(int)two_to(23-i));

printf(") * 2^%d\n", exponent);

/* convert this into decimal and print it out */

100

printf("%f = %d * %.12g * %f \n",

f,

(sign ? -1 : 1),

calc_float(significand, 0),

two_to(exponent));

105

/* do the math this time */

printf("%f = \%.12g \ n",

f,

(sign ? -1 : 1) *

110

calc_float(significand, 0) *

two_to(exponent)

);

return 0;

115 }

```

Sample output of the value 8.45, which we previously examined, is shown below.

```

Example 2.7. Analysis of 8 . 45

```

```

$ ./float 8.45

8.450000 = 1 * (1/2^0 + 1/2^5 + 1/2^6 + 1/2^7 + 1/2^10 + 1/2^11 + 1/2^14 + 1/2^15 + 8.450000 = 1 * (1/1 + 1/32 + 1/64 + 1/128 + 1/1024 + 1/2048 + 1/16384 + 1/32768 + 1

8.450000 = 1 * 1.05624997616 * 8.000000

8.450000 = 8.44999980927

```

From this example, we get some idea of how the inaccuracies creep into our floating point numbers.

This page titled 1.2: Types and Number Representation is shared under a CC BY-SA 3.0 license and was authored, remixed, and/or curated by Patrick McClanahan.

<sup>[3]</sup> Note that C99 also has portability helpers for printf . The PRI macros in <inttypes.h> can be used as specifiers for types of specified sizes. Again see the standard or pull apart the headers for full information.

<sup>[4]</sup> The ~ operator is the C language operator to apply NOT to the value. It is also occasionally called the one's complement operator, for obvious reasons now!

# **CHAPTER OVERVIEW**

# 2: The Basics - An Overview

- 2.1: Introduction to Operating Systems

- 2.2: Starting with the Basics

<sup>2:</sup> The Basics - An Overview is shared under a not declared license and was authored, remixed, and/or curated by LibreTexts.

## 2.1: Introduction to Operating Systems

## Introduction to Operating System

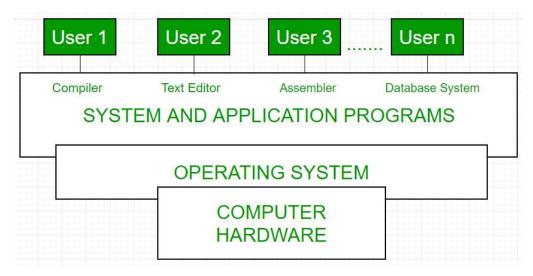

An operating system acts as an intermediary between the user of a computer and computer hardware. The purpose of an operating system is to provide an environment in which a user can execute programs in a convenient and efficient manner.

An operating system is a software that manages the computer hardware. The hardware must provide appropriate mechanisms to ensure the correct operation of the computer system and to prevent user programs from interfering with the proper operation of the system.

#### **Operating System**

#### Definition:

- An operating system is a program that controls the execution of application programs and acts as an interface between the user of a computer and the computer hardware.

- A more common definition is that the operating system is the one program running at all times on the computer (usually called the kernel), with all else being application programs.

- An operating system is concerned with the allocation of resources and services, such as memory, processors, devices, and information. The operating system correspondingly includes programs to manage these resources, such as a traffic controller, a scheduler, memory management module, I/O programs, and a file system.

#### **Functions of Operating system**

Operating system performs three functions:

- 1. Convenience: An OS makes a computer more convenient to use.

- 2. **Efficiency:** An OS allows the computer system resources to be used in an efficient manner.

- 3. **Ability to Evolve:** An OS should be constructed in such a way as to permit the effective development, testing and introduction of new system functions at the same time without interfering with service.

Operating system as User Interface –

- 1. User

- 2. System and application programs

- 3. Operating system

- 4. Hardware

Every general-purpose computer consists of the hardware, operating system, system programs, and application programs. The hardware consists of memory, CPU, ALU, and I/O devices, peripheral device, and storage device. System program consists of compilers, loaders, editors, OS, etc. The application program consists of business programs, database programs.

Figure 2.1.1: Conceptual view of a computer system ("Conceptual view of a computer system" by Unknown, Geeks for Geeks is licensed under CC BY-SA 4.0)

Every computer must have an operating system to run other programs. The operating system coordinates the use of the hardware among the various system programs and application programs for various users. It simply provides an environment within which other programs can do useful work.

The operating system is a set of special programs that run on a computer system that allows it to work properly. It performs basic tasks such as recognizing input from the keyboard, keeping track of files and directories on the disk, sending output to the display screen and controlling peripheral devices.

OS is designed to serve two basic purposes:

- 1. It controls the allocation and use of the computing System's resources among the various user and tasks.

- 2. It provides an interface between the computer hardware and the programmer that simplifies and makes feasible for coding, creation, debugging of application programs.

The Operating system must support the following tasks. The task are:

- 1. Provides the facilities to create, modification of programs and data files using an editor.

- 2. Access to the compiler for translating the user program from high level language to machine language.

- 3. Provide a loader program to move the compiled program code to the computer's memory for execution.

- 4. Provide routines that handle the details of I/O programming.

#### I/O System Management

One of the important jobs of an Operating System is to manage the operations of various I/O devices including mouse, keyboards, touch pad, disk drives, display adapters, USB devices, Bit-mapped screen, LED, Analog-to-digital converter, On/off switch, network connections, audio I/O, printers etc.

The I/O system of an OS works by taking I/O request from an application software and sending it to the physical device, which could be an input or output device then it takes whatever response comes back from the device and sends it to the application.

#### Components of I/O Hardware

- I/O Device

- Device Driver

- Device Controller

#### I/O Device:

I/O devices such as storage, communications, user-interface, and others communicate with the computer via signals sent over wires or through the air. Devices connect with the computer via ports, e.g. a serial or parallel port. A common set of wires connecting multiple devices is termed a bus.

I/O devices can be divided into two categories:

- Block devices A block device is one with which the device driver communicates by sending entire blocks of data. For example, Hard disks, USB cameras, Disk-OnKey etc.

- Character devices A character device is one with which the device driver communicates by sending and receiving single characters (bytes, octets). For example, serial ports, parallel ports, sounds cards etc

**Device Driver**: Device drivers are software modules that can be plugged into an OS to handle a particular device. Operating System takes help from device drivers to handle all I/O devices.

**Device Controller:** The Device Controller works like an interface between a device and a device driver. I/O units (Keyboard, mouse, printer, etc.) typically consist of a mechanical component and an electronic component where electronic component is called the device controller.

#### **History of Operating system**

Operating system has been evolving through the years. Following Table shows the history of OS.

| Generation | Year       | Electronic device used  | Types of OS Device |

|------------|------------|-------------------------|--------------------|

| First      | 1945-55    | Vacuum Tubes            | Plug Boards        |

| Second     | 1955-65    | Transistors             | Batch Systems      |

| Third      | 1965-80    | Integrated Circuits(IC) | Multiprogramming   |

| Fourth     | Since 1980 | Large Scale Integration | PC                 |

This page titled 2.1: Introduction to Operating Systems is shared under a CC BY-SA license and was authored, remixed, and/or curated by Patrick McClanahan.

## 2.2: Starting with the Basics

#### Processor

The processor is an important part of a computer architecture, without it nothing would happen. It is a programmable device that takes input, perform some arithmetic and logical operations and produce some output. In simple words, a processor is a digital device on a chip which can fetch instruction from memory, decode and execute them and provide results.

#### Basics of a Processor -

A processor takes a bunch of instructions in machine language and executes them, telling the processor what it has to do. Processors performs three basic operations while executing the instruction:

- 1. It performs some basic operations like addition, subtraction, multiplication, division and some logical operations using its Arithmetic and Logical Unit (ALU).

- 2. Data in the processor can move from one location to another.

- 3. It has a Program Counter (PC) register that stores the address of next instruction based on the value of PC.

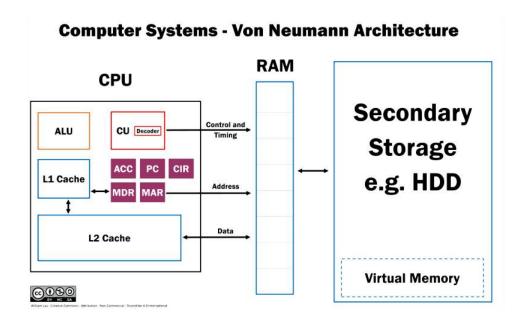

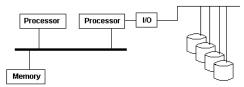

A typical processor structure looks like this.

Figure 2.2.1: Von Neumann Architecture. ("File:Computer Systems - Von Neumann Architecture Large poster anchor chart.svg" by BotMultichillT, Wikimedia Commons is licensed under CC BY-NC-SA 4.0)

#### **Basic Processor Terminology**

#### Control Unit (CU)

A control unit (CU) handles all processor control signals. It directs all input and output flow, fetches the code for instructions and controlling how data moves around the system.

### Arithmetic and Logic Unit (ALU)

The arithmetic logic unit is that part of the CPU that handles all the calculations the CPU may need, e.g. Addition, Subtraction, Comparisons. It performs Logical Operations, Bit Shifting Operations, and Arithmetic Operation.

#### • Main Memory Unit (Registers)

- 1. **Accumulator (ACC):** Stores the results of calculations made by ALU.

- 2. **Program Counter (PC):** Keeps track of the memory location of the next instructions to be dealt with. The PC then passes this next address to Memory Address Register (MAR).

- 3. **Memory Address Register (MAR):** It stores the memory locations of instructions that need to be fetched from memory or stored into memory.

- 4. **Memory Data Register (MDR):** It stores instructions fetched from memory or any data that is to be transferred to, and stored in, memory.

- 5. **Current Instruction Register (CIR):** It stores the most recently fetched instructions while it is waiting to be coded and executed.

- 6. **Instruction Buffer Register (IBR):** The instruction that is not to be executed immediately is placed in the instruction buffer register IBR.

- **Input/Output Devices** Program or data is read into main memory from the *input device* or secondary storage under the control of CPU input instruction. *Output devices* are used to output the information from a computer.

- **Buses** Data is transmitted from one part of a computer to another, connecting all major internal components to the CPU and memory, by the means of Buses. Types:

- 1. Data Bus (Data): It carries data among the memory unit, the I/O devices, and the processor.

- 2. Address Bus (Address): It carries the address of data (not the actual data) between memory and processor.

- 3. **Control Bus (Control and Timing):** It carries control commands from the CPU (and status signals from other devices) in order to control and coordinate all the activities within the computer.

## Memory

Memory attached to the CPU is used for storage of data and instructions and is called internal memory. The internal memory is divided into many storage locations, each of which can store data or instructions. Each memory location is of the same size and has an address. With the help of the address, the computer can read any memory location easily without having to search the entire memory, when a program is executed, it's data is copied to the internal memory and is stored in the memory till the end of the execution. The internal memory is also called the Primary memory or Main memory. This memory is also called as RAM, i.e. Random Access Memory. The time of access of data is independent of its location in memory, therefore this memory is also called Random Access memory (RAM).

#### I/O Modules

The method that is used to transfer information between main memory and external I/O devices is known as the I/O interface, or I/O modules. The CPU is interfaced using special communication links by the peripherals connected to any computer system. These communication links are used to resolve the differences between CPU and peripheral. There exists special hardware components between CPU and peripherals to supervise and synchronize all the input and output transfers that are called interface units.

#### Mode of Transfer:

The binary information that is received from an external device is usually stored in the memory unit. The information that is transferred from the CPU to the external device is originated from the memory unit. CPU merely processes the information but the source and target is always the memory unit. Data transfer between CPU and the I/O devices may be done in different modes.

Data transfer to and from the peripherals may be done in any of the three possible ways

- 1. **Programmed I/O:** is the result of the I/O instructions written in the program's code. Each data transfer is initiated by an instruction in the program. Usually the transfer is from a CPU register and/or memory. In this case it requires constant monitoring by the CPU of the peripheral devices.

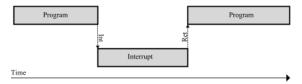

- 2. Interrupt- initiated I/O: using an interrupt facility and special commands to issue an interrupt request signal whenever data is available from any device. In the meantime the CPU can proceed processing other programs. The interface meanwhile keeps monitoring the device. When it is determined that the device is ready for a data transfer it initiates an interrupt request signal to the CPU. Upon detection of an external interrupt signal the CPU momentarily stops the task it was processing, and services program that was waiting on the interrupt to process the I/O transfer> Once the interrupt is satisfied, the CPU then return to the task it was originally processing.

- 3. **Direct memory access( DMA)**: The data transfer between a fast storage media such as magnetic disk and main memory is limited by the speed of the CPU. Thus we can allow the peripherals directly communicate with each other using the memory buses, removing the intervention of the CPU. This type of data transfer technique is known as direct memory access, or DMA. During DMA the CPU is idle and it has no control over the memory buses. The DMA controller takes over the buses to manage the transfer directly between the I/O devices and the memory unit.

### Adapted from:

"Introduction of Microprocessor" by DikshaTewari, Geeks for Geeks is licensed under CC BY-SA 4.0

"Last Minute Notes Computer Organization" by Geeks for Geeks is licensed under CC BY-SA 4.0

"Functional Components of a Computer" by aishwaryaagarwal2, Geeks for Geeks is licensed under CC BY-SA 4.0

"System Bus Design" by deepak, Geeks for Geeks is licensed under CC BY-SA 4.0

"I/O Interface (Interrupt and DMA Mode)" by Unknown, Geeks for Geeks is licensed under CC BY-SA 4.0

This page titled 2.2: Starting with the Basics is shared under a CC BY-SA license and was authored, remixed, and/or curated by Patrick McClanahan.

# **CHAPTER OVERVIEW**

### 3: The Operating System

- 3.1: The Role of the Operating System

- 3.2: Operating System Organisation

- 3.3: System Calls

- 3.4: Privileges

- 3.5: Function of the Operating System

- 3.6: Types of Operating Systems

- 3.6.1: Types of Operating Systems (continued)

- 3.6.2: Types of Operating Systems (continued)

- 3.7: Difference between multitasking, multithreading and multiprocessing

- 3.7.1: Difference between multitasking, multithreading and multiprocessing (continued)

- 3.7.2: Difference between Multiprogramming, multitasking, multithreading and multiprocessing (continued)

<sup>3:</sup> The Operating System is shared under a not declared license and was authored, remixed, and/or curated by LibreTexts.

### 3.1: The Role of the Operating System

## The role of the operating system

The operating system underpins the entire operation of the modern computer.

#### Abstraction of hardware

The fundamental operation of the operating system (OS) is to abstract the hardware to the programmer and user. The operating system provides generic interfaces to services provided by the underlying hardware.

In a world without operating systems, every programmer would need to know the most intimate details of the underlying hardware to get anything to run. Worse still, their programs would not run on other hardware, even if that hardware has only slight differences.

### Multitasking

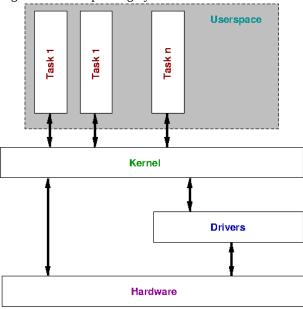

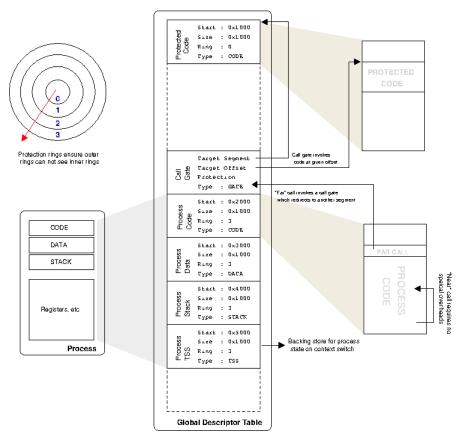

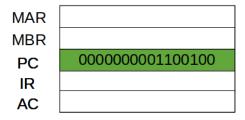

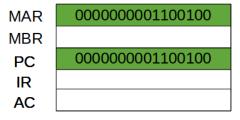

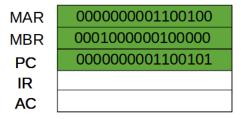

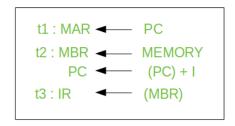

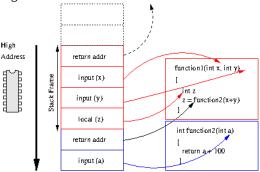

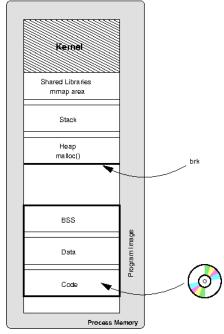

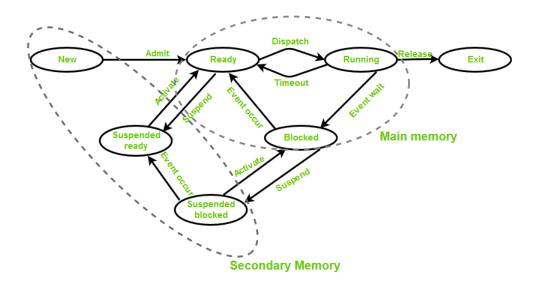

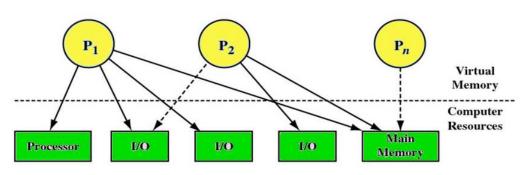

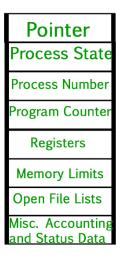

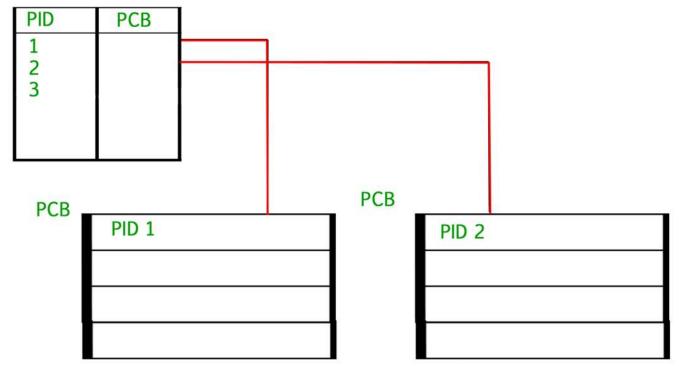

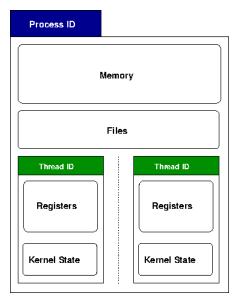

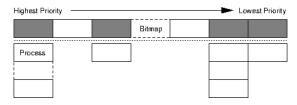

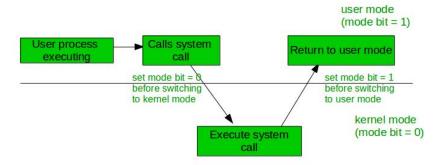

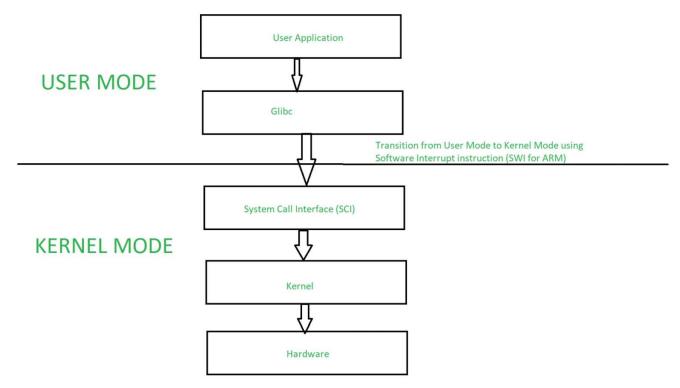

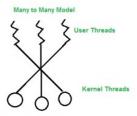

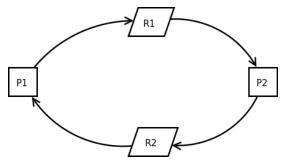

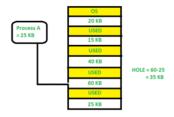

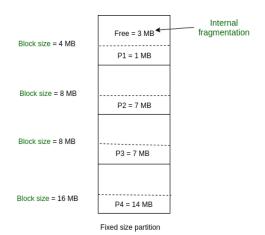

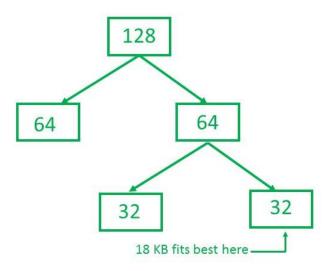

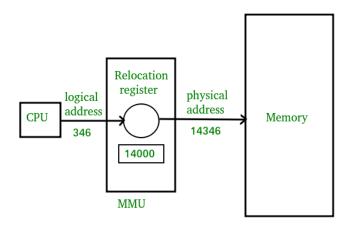

We expect modern computers to do many different things at once, and we need some way to arbitrate between all the different programs running on the system. It is the operating systems job to allow this to happen seamlessly.