## **Power Electronics**

This book has been prepared with the financial support of European Union. Authors from Riga Technical University and University of Leuven (KU Leuven - Katholieke Universiteit Leuven), and both Universities are responsible for the content of this document. This publication reflects the views only of the authors, and it can not be regarded as the European Union's official position.

The book is developed in a frame of the project "Development of Training Network for Improving Education in Energy Efficiency" acronym: ENERGY, grant Nr. 530379-TEMPUS-1-2012-1-LVTEMPUS-JPCR.

Project was approved by the European Commission in frame of the Program Tempus IV – Fifth call for proposals (Programme guide EACEA/25/2011).

Sub-programme: Joint Projects

**Action:** Curricular Reform

**Deliverable:** 2.1 Development and translation of study courses within the frame of direction

of Power Electronics.

Project Scientific Manager: Leonids Ribickis

Project Manager: Anatolijs Zabašta

Editors: Leonids Ribickis, Anastasija Zhiravecka

Coordinator institution: Riga Technical University

### **Contributors**

**Anastasija Zhiravecka**, associate professor, senior researcher, electrical engineering. IEEI: Riga Technical Univ., Faculty of Power and Electrical Engineering, Institute of Industrial Electronics and Electrical Engineering, 1, Kronvalda bulv. off. 202, Riga, LV 1050, Latvia, tel. +371 67089917, Zhiravecka@eef.rtu.lv

**Dries Vanoost**, PhD researcher, electrical engineering, KU Leuven university, Faculty of Engineering Technology, KU Leuven@Kulab, ReMI research group, Zeedijk 101, B-8400 Oostende, Belgium. tel. +32 (0) 59 56 90 23, dries.vanoost@kuleuven.be

**Ilja Galkins**, professor, senior researcher, IEEI: Riga Technical Univ., Faculty of Power and Electrical Engineering, Institute of Industrial Electronics and Electrical Engineering, 1, Kronvalda bulv., Riga, LV 1050, Latvia, tel. +371 67089917, gia@eef.rtu.lv

**Ivars Rankis**, professor, senior researcher, electrical engineering. IEEI: Riga Technical Univ., Faculty of Power and Electrical Engineering, Institute of Industrial Electronics and Electrical Engineering, 1, Kronvalda bulv. off. 202, Riga, LV 1050, Latvia, tel. +371 67089917, rankis@eef.rtu.lv

**Joan Peuteman**, docent, electrical engineering, KU Leuven university, Faculty of Engineering Technology, KU Leuven@Kulab, ReMI research group, Zeedijk 101, B-8400 Oostende, Belgium. tel. +32 (0)59 56 90 23, joan.peuteman@kuleuven.be

**Leonids Ribickis**, Prof., Dr. habil.sc. ing. Leonids Ribickis is a rector of Riga Technical University (RTU), director of Institute of Industrial Electronics and Electrical engineering, Faculty of Power and Electrical Engineering, RTU, and a scientific head of Electromechatronics Scientific Laboratory, 1, Kalku Str. off. 217, Riga, LV 1658, Latvia, tel. +371 67089300, Leonids.Ribickis@rtu.lv

## Content

| Introduction                                                                           | 7  |

|----------------------------------------------------------------------------------------|----|

| 1. Semiconductor Devices in Power Electronics                                          | 10 |

| 1.1. Diodes                                                                            | 11 |

| 1.2. Thyristors                                                                        | 14 |

| 1.3. Transistors                                                                       | 20 |

| 1.3.1. Powerful Field Effect Transistors                                               | 24 |

| 1.3.2. Bipolar transistors with insulated base (IGBT)                                  | 26 |

| 1.4. Power losses                                                                      | 28 |

| 1.5. Comparison of Semiconductor Devices                                               | 30 |

| 2. Hard-Switching DC-DC Converters                                                     | 32 |

| 2.1. Fundamentals of Hard-Switching DC/DC Converters                                   | 33 |

| 2.1.1. Quasi-Stationary Mode                                                           | 33 |

| 2.1.2. Operation of Semiconductor Elements in Hard-Switching Converters                | 34 |

| 2.1.3. Operation of Inductors and Capacitors in Quasi-Stationary Mode                  | 35 |

| 2.1.4. Open and Closed Loop Operation                                                  | 36 |

| 2.1.5. Types of DC/DC Converters                                                       | 37 |

| 2.2. DC/DC converters with energy transferring magnetic element                        | 37 |

| 2.2.1. Genesis of basic DC/DC converters with energy transferring inductor             | 37 |

| 2.2.2. Static operation of DC/DC converters with energy transferring inductor          | 41 |

| 2.2.3. Chuk converter                                                                  | 54 |

| 2.2.4. SEPIC converter                                                                 | 56 |

| 2.2.5.ZETA converter                                                                   | 57 |

| 2.3. Multi-quadrant DC/DC converters                                                   | 58 |

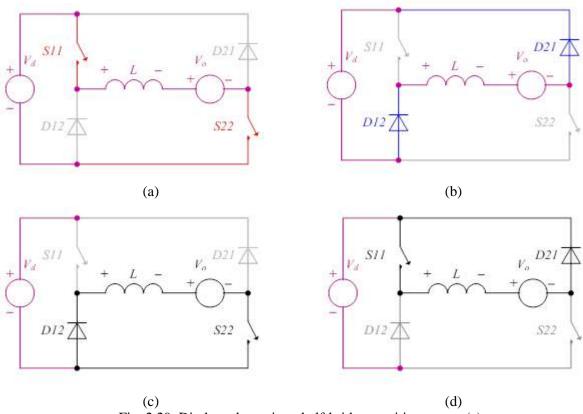

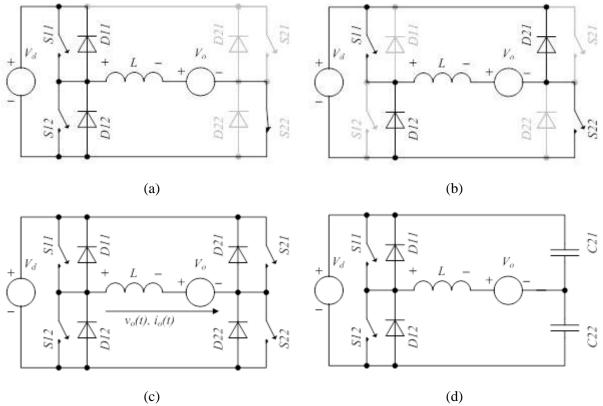

| 2.3.1. Synchronous buck converter – bidirectional output current                       | 58 |

| 2.3.2. Diode and transistor half-bridge converter – bidirectional output voltage.      | 59 |

| 2.3.3.Full-Bridge and Capacitor Half-Bridge Converters – Bidirectional Outpand Current | _  |

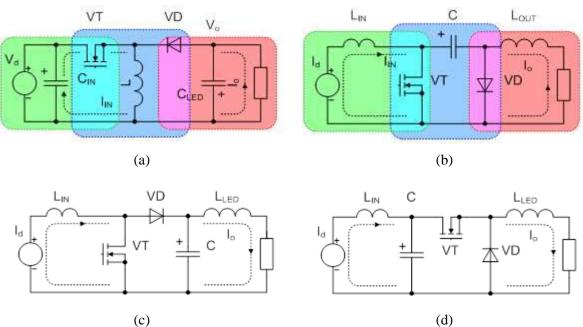

| 2.4. Current fed converters                                                            | 62 |

| 2.4.1. Synthesis of Current Fed Converters                                             | 62 |

| 2.4.2 Static Model of CE Convertors                                                    | 62 |

| 3. Rectifiers                                           | 65     |

|---------------------------------------------------------|--------|

| 3.1. Introduction                                       | 66     |

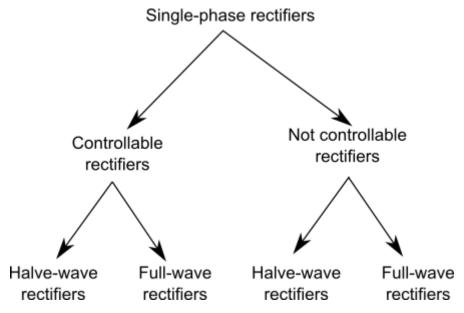

| 3.2. Single-phase rectifiers                            | 66     |

| 3.2.1. Single-phase uncontrollable rectifiers           | 67     |

| 3.2.2. Single-phase controllable rectifiers             | 75     |

| 3.3. Three-phase rectifiers                             | 109    |

| 3.3.1. Three-phase uncontrollable rectifiers            | 110    |

| 3.3.2. Three phase line-commutated diode rectifiers     | 112    |

| 3.3.3. Three phase line-commutated thyristor rectifiers | 120    |

| 3.3.4. Active Front End                                 | 135    |

| 4. Inverters                                            | 147    |

| 4.1. Introduction                                       |        |

| 4.2. Single-phase Voltage Source inverter               | 149    |

| 4.2.1. Half-bridge VSI                                  | 149    |

| 4.2.2. Single-phase full-bridge VSI                     | 161    |

| 4.3. Three phase inverters                              |        |

| 4.3.1. square wave type Voltage Source Inverter         |        |

| 4.3.2. Pulse Frequency converter                        |        |

| 4.3.3. Pulse Width Modulation                           | 176    |

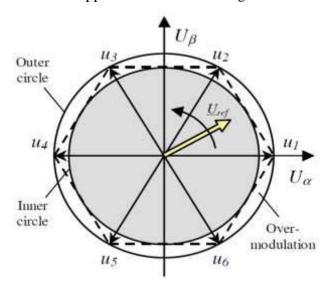

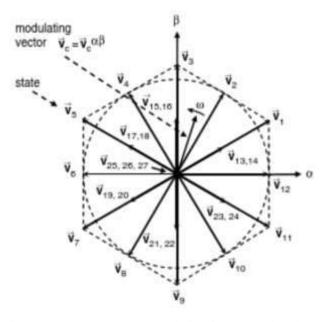

| 4.4. Space-vector modulation                            | 179    |

| 4.4.1. Clarke Transformation                            | 179    |

| 4.4.2. Eight possible states                            |        |

| 4.4.3. Making the PWM signal                            | 184    |

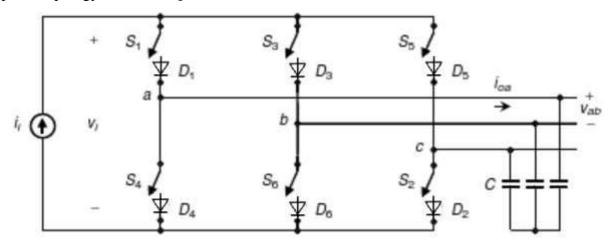

| 4.5. CSI                                                |        |

| 4.6. Voltage source based multilevel topologies         | 189    |

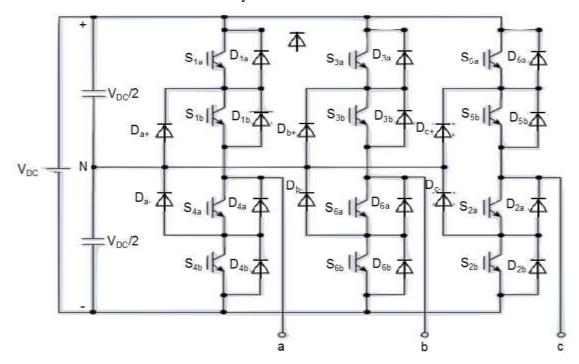

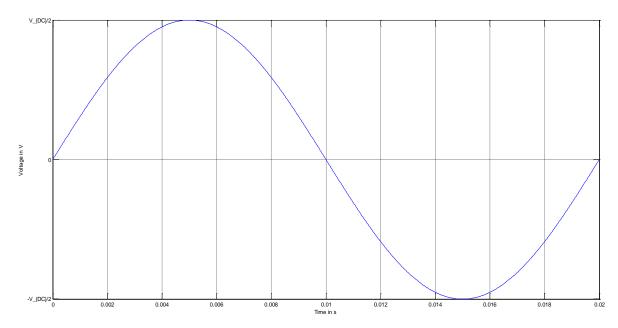

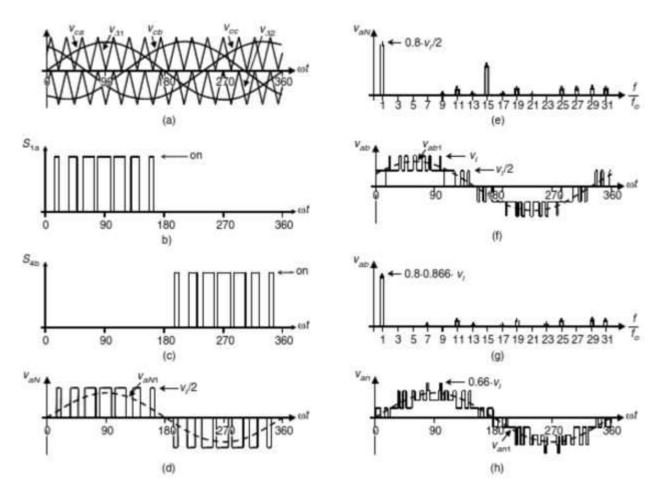

| 4.6.1. The sinusoidal PWM technique for three-level V   | 'SI191 |

| 4.6.2. The sinusoidal PWM technique for N-level VSI     | 193    |

| 4.6.3. Space-vector modulation in three-level VSI       | 194    |

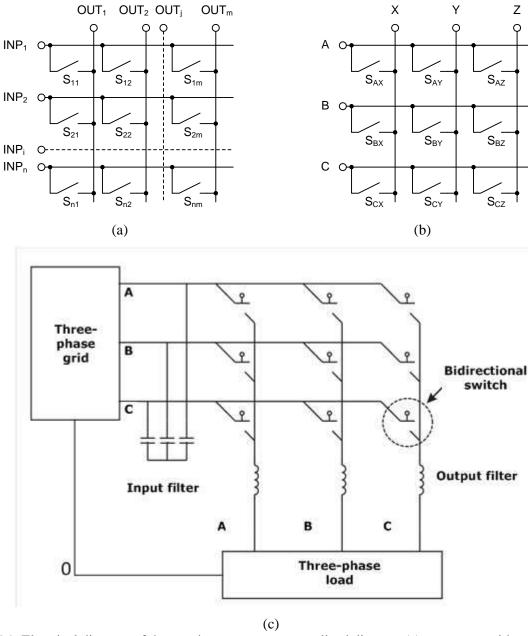

| 5. Matrix Converters                                    | 195    |

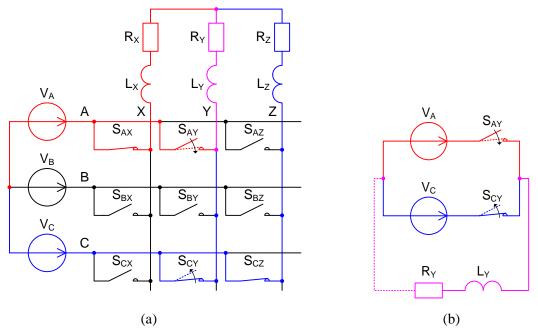

| 5.1. Configuration of Matrix Converters                 | 196    |

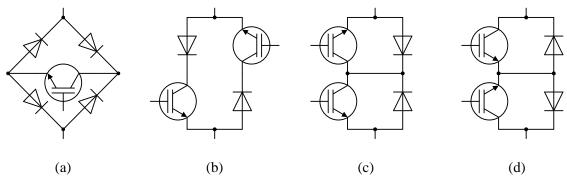

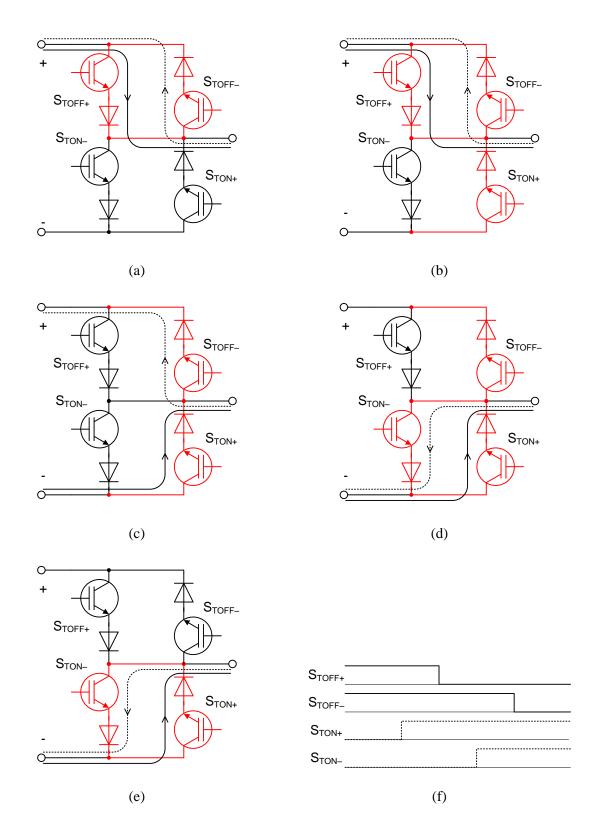

| 5.2. Electronic Switches                                | 197    |

| 5.3. Commutation of switches in MC                      | 198    |

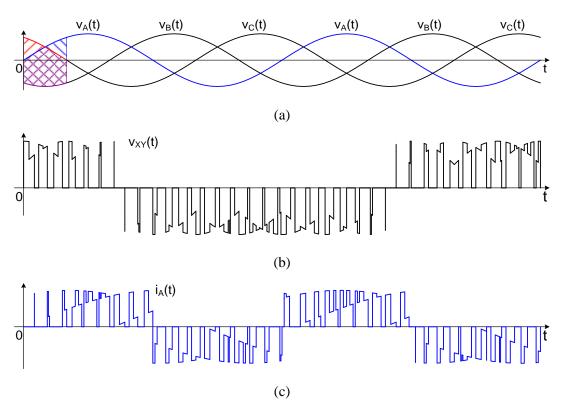

| 5.4. Control of MC                                      | 200    |

| 6. | Snubber Circuits and Soft-Switching Converters                                    | 203 |

|----|-----------------------------------------------------------------------------------|-----|

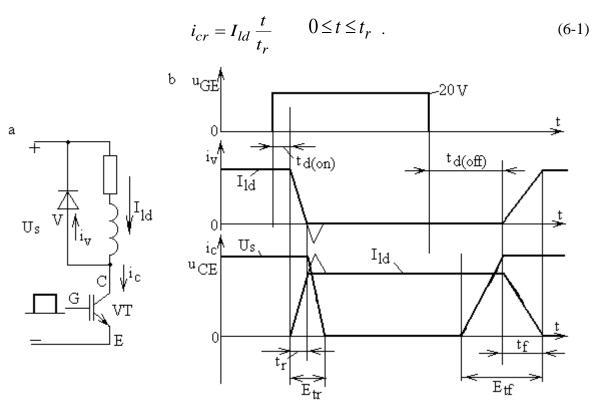

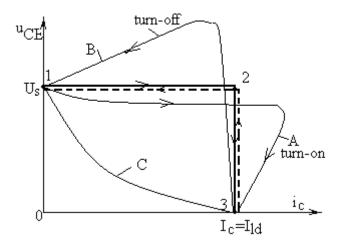

| (  | 6.1. Switching Trajectory                                                         | 204 |

|    | 6.1.1. The Really Operation Conditions of a Switch in Converter Scheme            | 204 |

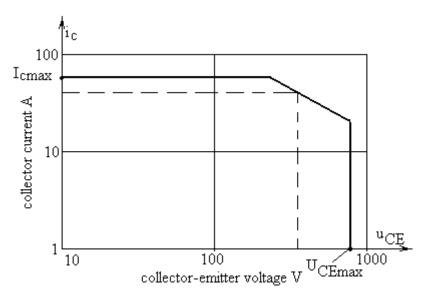

|    | 6.1.2. Safe Operating Area and switching process trajectory                       | 207 |

| (  | 5.2. Snubber Circuits                                                             | 209 |

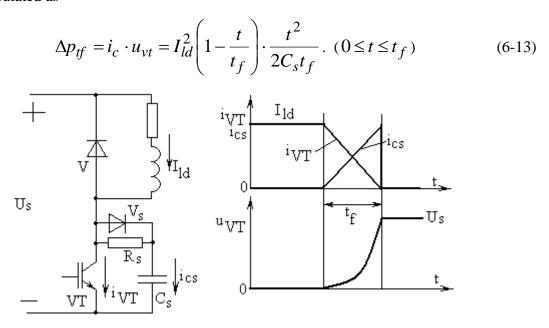

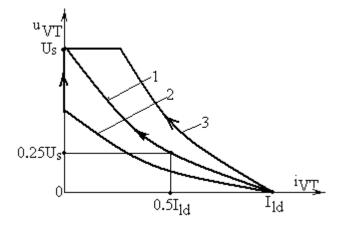

|    | 6.2.1. Snubber circuits for improving a turn-off process of switching transistor  | 209 |

|    | 6.2.2. Improvement of turn-on process of switching transistor                     | 214 |

| (  | 5.3. Soft-switching Converters                                                    | 216 |

|    | 6.3.1. Zero Current (ZC) and Zero Voltage (ZC) Commutation                        | 216 |

|    | 6.3.2. Soft commutated converters                                                 | 222 |

| (  | 6.4. Resonant and Quasi-Resonant Converters                                       | 224 |

|    | 6.4.1. Quasi-Resonant QR converters                                               | 224 |

|    | 6.4.2. Zero-Voltage transition converter                                          | 229 |

|    | 6.4.3. Resonant Converters                                                        | 231 |

| 7. | Selected Topics in Power Electronics                                              | 236 |

|    | 7.1. Power Electronics in Energy Transmission                                     | 237 |

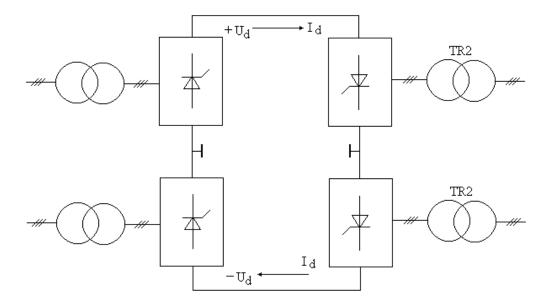

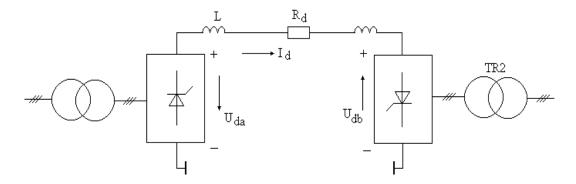

|    | 7.1.1. General construction of the system                                         | 237 |

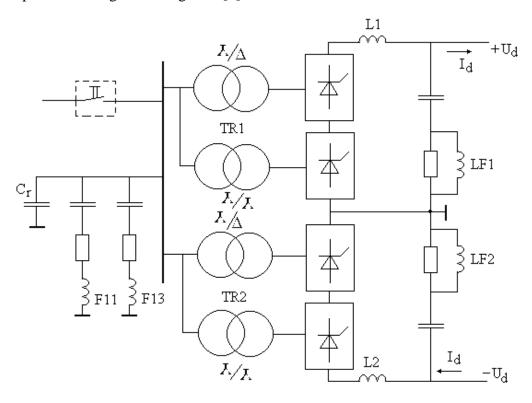

|    | 7.1.2. Practical realization of the thyristor DC transmission system              | 239 |

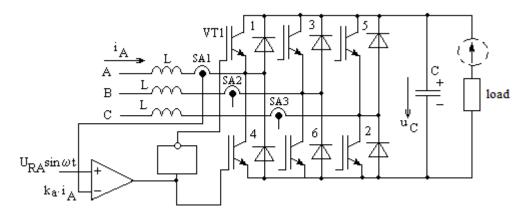

|    | 7.1.3. DC transmission with transistor converters                                 | 242 |

|    | 7.1.4. The practical realization of the system.                                   | 245 |

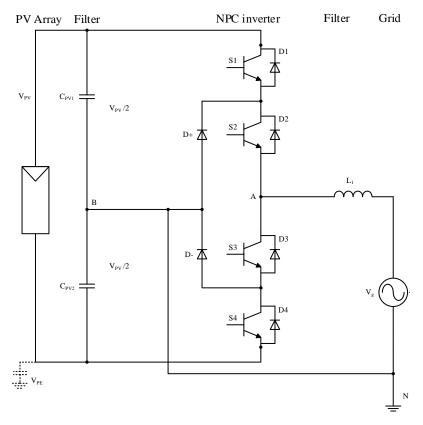

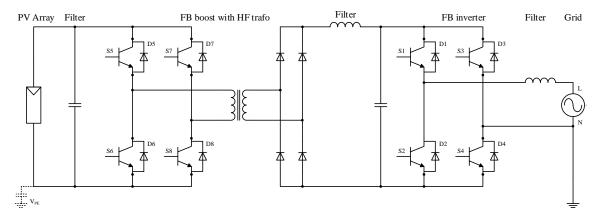

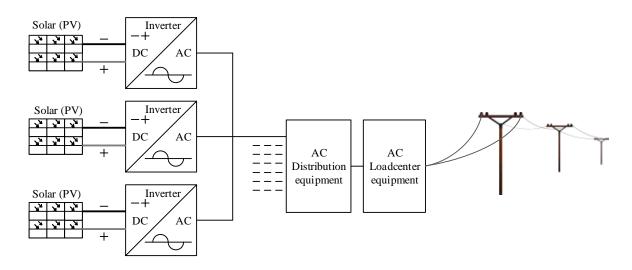

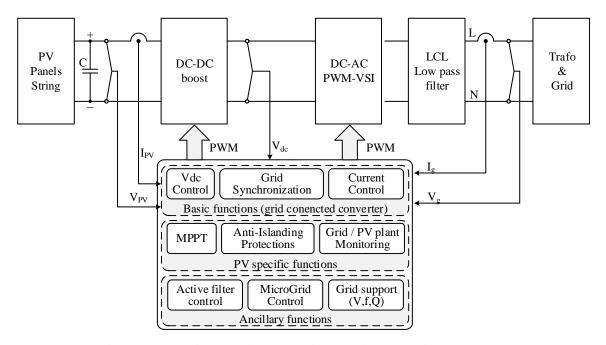

|    | 7.2. Power Electronics in Renewable Energy Production                             | 246 |

|    | 7.2.1. Renewable Energy Sources                                                   | 246 |

|    | 7.2.2. Renewable Electrical Energy production plants and systems                  | 246 |

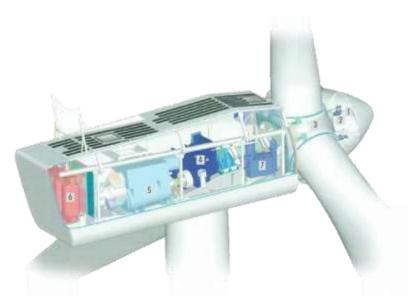

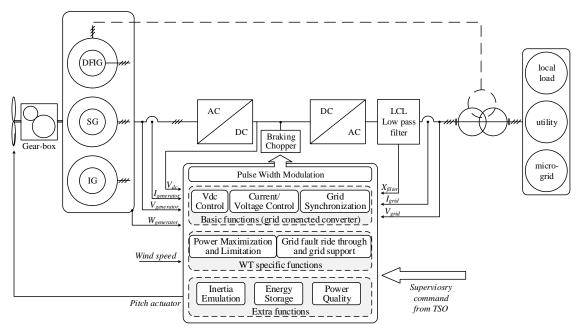

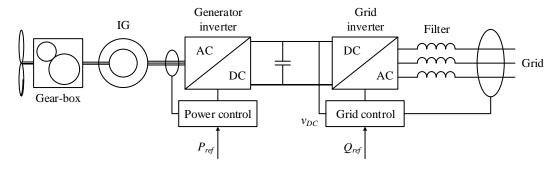

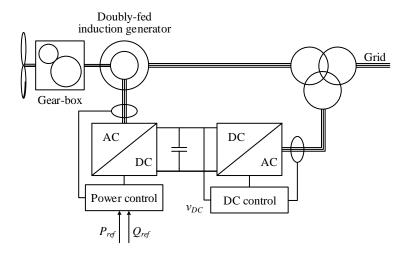

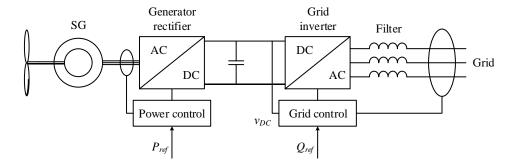

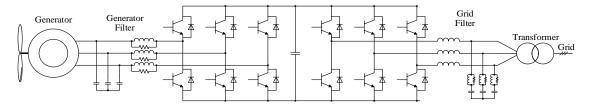

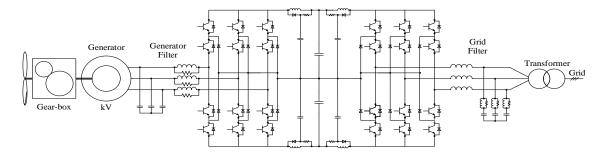

|    | 7.2.3. Power electronic converters for wind turbines                              | 252 |

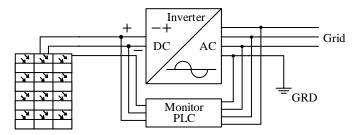

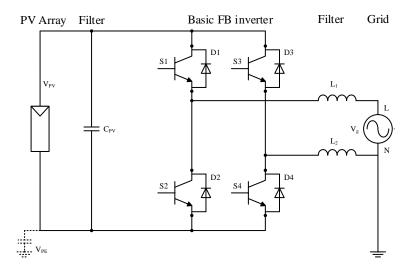

|    | 7.2.4. Power electronic converters for solar PV plants                            | 257 |

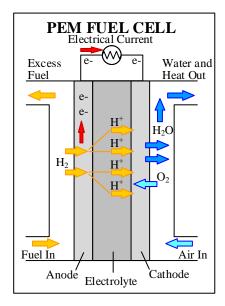

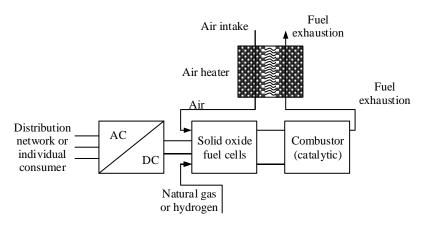

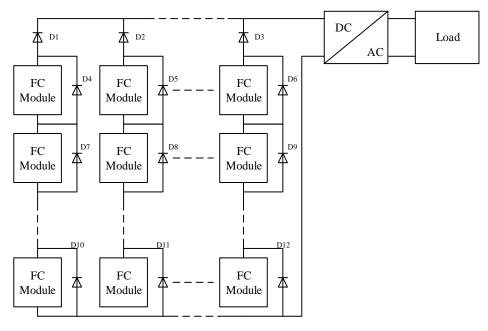

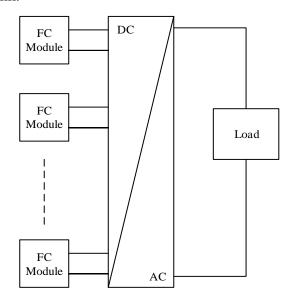

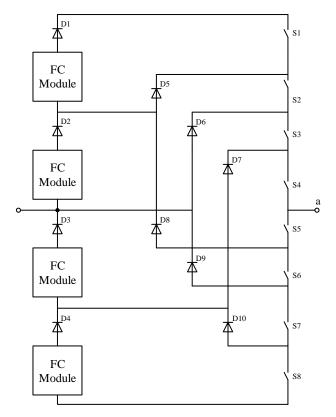

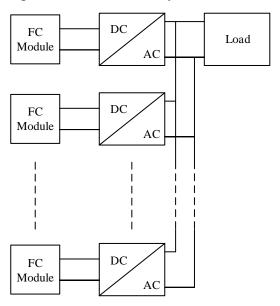

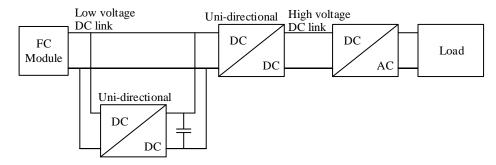

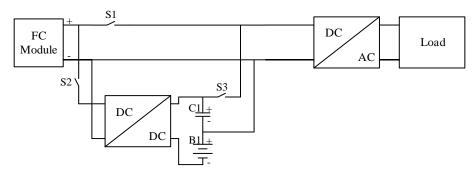

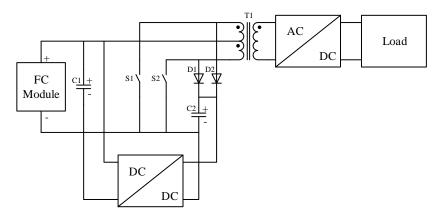

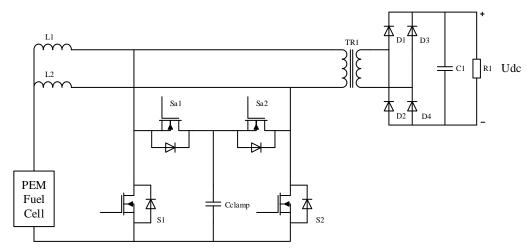

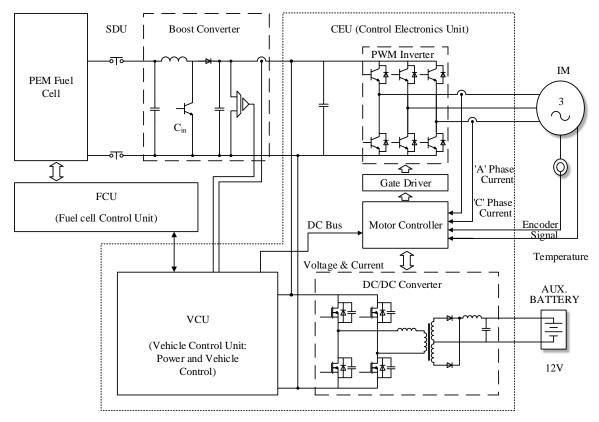

|    | 7.2.5. Power electronics for power plants with Fuel Cells                         | 263 |

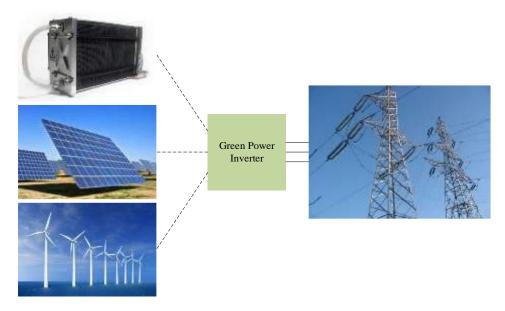

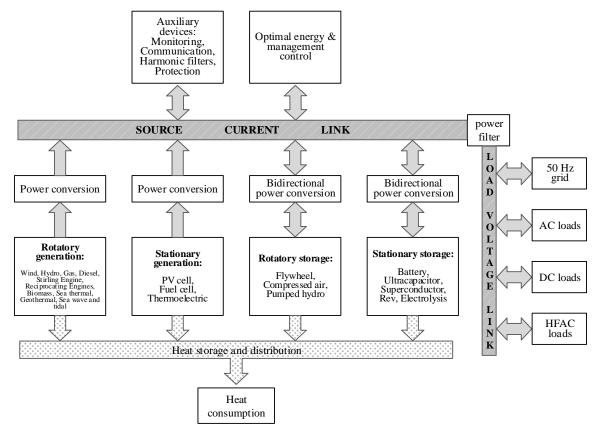

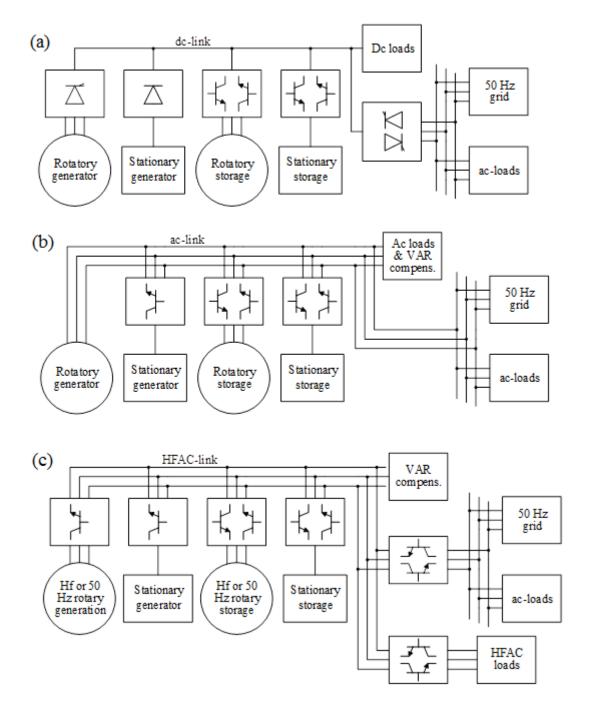

|    | 7.2.6. Power electronics in the integrated renewable sources of electrical energy | 271 |

|    | References                                                                        | 276 |

### Introduction

Electrical Energy flow control and type change (AC  $\leftrightarrow$  DC) is an important scientific and engineering task – starting from the installation of electrical supply systems to wide usage of electricity in industries, transport and households – for more than 100 years. Due to semiconductor revolution, nowadays electromechanical and electromagnetic transformers are being replaced with advanced Power Electronic Converters with a very high efficiency. We can find Power Electronic Equipment with power amplitude starting from some watts to many megawatts in any urbanized and industrialized area of the World.

What is Power Electronics? An adequate definition [1] is provided by Prof. R. W. De Doncker, (RWTH Aachen):

"Power Electronics deals with the control and the low-loss conversion of electrical energy using electrical switches, nowadays – power semiconductors."

Basically we have two types of electrical energy: Direct Current (DC) and Alternating Current (AC). Both have different possible electrical potential (with a volume of some volts to gigavolts). Load supply with necessary electrical energy type, voltage and frequency (in case of AC supply) is the responsibility of Power Electronic Converters.

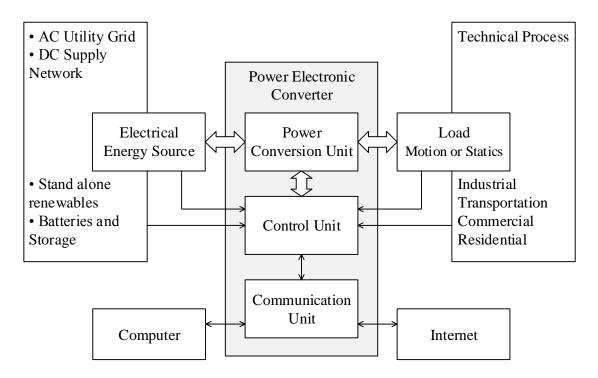

Fig.1. Power Electronic System

As it can be seen in Fig.1., Power Electronic System is complicated. The main Power Electronic Converter unit provides power flow conversion (AC to DC or DC to AC) and adjustment (for voltage and frequency regulation). The Control Unit is organizing an appropriate signal distribution to semiconductor power switches and implements control algorithms of converter. The Control Unit also is observing energy source and load conditions on real time and, of course, is following the commands from Communication Unit. In a large

and complex process or production control system, Power Electronic Equipment is only one element.

Application possibilities of Power Electronics are everywhere around us, starting from mobile telephones, cars, ships, trains, airplanes, domestic appliances, commercial buildings to all industries and military applications.

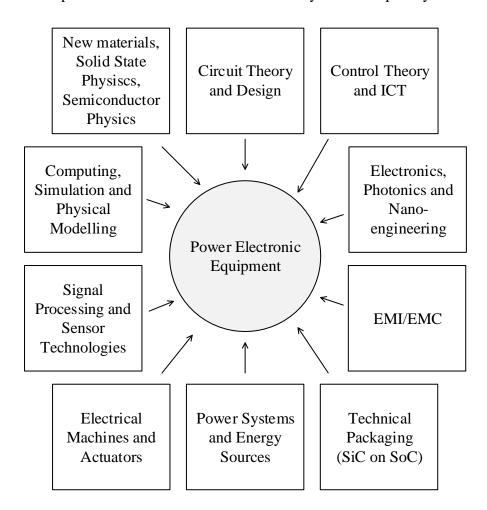

The development of Power Electronic Converters in a broader scope started after the invention of transistor in 1957. Main topologies of AC-DC, DC-AC and DC-DC converters were invented and designed at the beginning of 60's. But today the improvement of Power Electronic Converter efficiency is carried on in many research centers and companies all over the World. Development of an efficient converter is a very multidisciplinary task.

Fig.2. Multidisciplinarity of Power Electronic Technology

Fig.2. shows some research and development areas, which significantly influence Power Electronic Converter technology.

People in the World are more and more using electrical energy, fossil sources are limited, new alternative energy production technologies are being developed and it can be possible only with a wide usage of Power Electronic Converters. Therefore it is declared that Power Electronics is the main technology for the 21<sup>st</sup> century.

All contributors of this book are willing to explain the reader several topics of Power Electronic technology.

The first chapter describes basics of semiconductor devices in Power Electronics.

The second chapter more precisely explains DC-DC Converter operation at hard switching mode.

The third part of the book is devoted to rectifiers – the most applied Power Electronic Converters.

A very detailed explanation of topologies and control methods of inverters is given in the fourth chapter – Power Electronic Converters of DC to AC.

The fifth chapter is more specific and covers the basics of Matrix Converters.

In the sixth chapter snubber circuit meaning and some converter switching methods, including soft-switching, are explained.

Some application areas of Power Electronic Converters are described in chapter 7 including energy transmission and renewable energy production.

<sup>1.</sup> De Doncker R.W. Lecture Notes: Power Electronics // Koln: Hundt Druck Gmbh, 2009 – 206p.

Anastasija Žiravecka

Riga Technical University, Latvia

### 1.1. Diodes

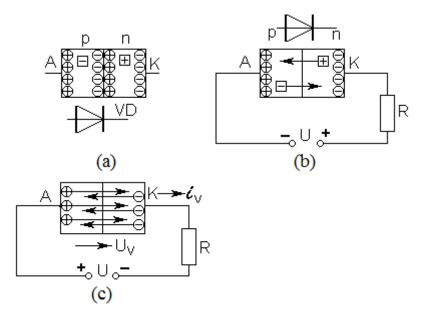

Diode is a semiconductor structure of two silicium layers of different conductivity: one layer (left) contains more positively charged (p) particles (Fig.1.1), the other (right) - more negatively charged (n) particles. This p-n joint is called bipolar.

The majority of the charges are obtained by means of adding to the silicium structure other active materials. Therefore both layers contain additional charges of opposite polarity - minor charges. In the neutral condition of the structure a part of p major charges move to n layer, but a part of n major charges - to the p layer.

Fig. 1.1. The operation of the diode structure in neutral (a), reverse (b) and direct (c) bias modes.

But crossing the barrier the further moving of p charges is slowing down because of impact of n layer negative charges crossing the barrier and getting to n layer. Similar situation takes place with n charges crossing the barrier. It produces the difference of potentials across the barrier - 0.7 V.

In the case when p layer is connected to the negative terminal of the source, n layer - to the positive one, the structure is in the mode of reverse bias, when the barrier provides very low conducting zone for the majority charges. The current is close to zero and depends on the flow of minority charges. The voltage of this polarity is reverse biasing voltage, but the current - a leakage current.

If the reverse biasing voltage is increasing the leakage current is also increasing. With some high enough voltage (hundreds of volts) the increasing of the leakage current results in high power losses and increasing of p-n structure temperature to the maximum acceptable. Exceeding of this temperature causes irreversible braking of the p-n junction - thermal breakdown.

The intensity of minority carriers' movement in the mode of reverse bias depends a lot on the heating regime of the diode, influence of light and radiation on the junction. If p layer is connected to the positive terminal of the source, but n layer - to the negative, the majority carriers start to flow through the barrier producing the electric current.

$$I_{\nu} = \frac{U - U_{\nu}}{R} \quad , \tag{1-1}$$

where  $U_V$  is the voltage drop across the diode, higher that the difference of potentials across the barrier. The current in the circuit will exist also only if the supply voltage is higher that that of the barrier.

The arrow in the symbol of diode is directed from p to n layer and defines the possible direction of the operation current, from anode A to cathode K.

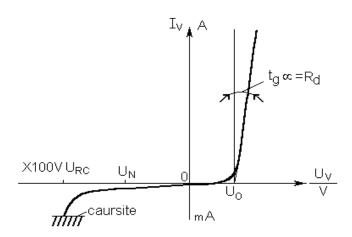

Fig.1.2 demonstrates the volt-ampere characteristics of the diode, i.e. the dependence of the current on the voltage across A and K. In the quadrant of the direct bias the grade of measurement unit of the current is usually amperes, but voltage - from zero to 2-2.5 V. In the reverse bias quadrant the current is measured in milliamperes, but the voltage - hundreds of volts. The volt-ampere characteristic of the direct bias can be linearised as

$$U_V = U_0 + I_V R_d \quad , \tag{1-2}$$

where  $U_0$  - is so-called threshold voltage (about 0.9 V),  $R_d$  - dynamic (differential) resistance of the diode.

Fig. 1.2. Volt-ampere characteristics of the diode

This linearised characteristic is of top importance for the calculations of power losses of the devices. If the diode is connected into the scheme like in fig.1.3 and its instantaneous value of the current within the time interval from 0 to  $\pi$  is  $i_v = I_m \sin \omega t$ , the average power losses per period are calculated as the following

$$\Delta P_{vvid} = \frac{1}{2\pi} \int_{0}^{\pi} I_{m} \sin \omega t \cdot (U_{0} + R_{d}I_{m} \cdot \sin \omega t) d\omega t = \frac{I_{m}U_{0}}{\pi} + \frac{I_{m}^{2}}{4} R_{d} = I_{vid} \cdot U_{0} + I_{ef}^{2} R_{d} . \quad (1-3)$$

This is a typical expression for these calculations. The calculated power losses define the temperature of the diode structure in the stationary regime

$$\theta_{pn} = \theta_0 + \Delta P_{Vvid} \cdot R_T, \tag{1-4}$$

where  $\theta_0$  - is an ambient temperature,  $R_T$  - thermal resistance of the structure and cooling system ( $^0C$  / W). To avoid the damage of the structure the temperature of it  $\theta_{pn}$  should not exceed the value of about  $130^0C$ .

With the known parameters  $R_T$ ,  $R_d$ ,  $U_o$  assuming  $\theta_{pn}$  and  $\theta_0$  the acceptable current of the diode can be calculated, i.e. the average value of the current through the diode:

$$I_{dp} = \frac{-2U_0 + 2\sqrt{U_0^2 + \frac{(\Theta_{pn} - \Theta_0)\pi^2 R_d}{R_T}}}{\pi^2 R_d} . \tag{1-5}$$

The lower is resistance  $R_T$ , i.e. the cooling system is better, the higher is current  $I_{dp}$ . If rated  $R_T$ ,  $\theta_{pn}$ ,  $\theta_0$  are assumed this expression gives an opportunity to obtain the rated current of the diode.

The rated voltage of the diode  $U_{RC}$  is assumed of about half of the diode breakdown voltage. For example, if  $U_{RC}$  = 1550 V, then  $U_{N}$  = 700 V, the diode is of class 7 according to the assumed voltage.

The breakdown is determined with the instant value of voltage therefore with the reverse voltage amplitude. If the circuit of the diode is connected to 220V AC source then the amplitude of this voltage higher than 300V should be taken into account. Then in this case a diode of the 4<sup>th</sup> class should be chosen.

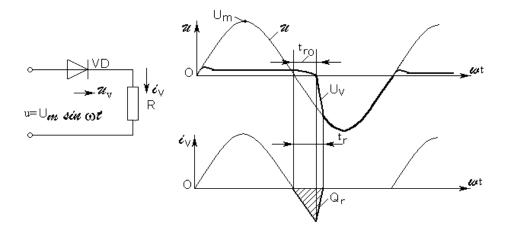

Dynamic operation regime of the diode is also of top importance at the beginning and end of the periods of current control. At the beginning some increasing of the direct voltage drop is typical for the structure, at the end (Fig.1.3) at some time moment  $t_{r0}$  the diode conducts full current in the reverse biasing mode.

The latter regime is explained with the increased concentration of the majority carriers of opposite polarity in the correspondent layers of the diode during the period of the current conduction (n polarity in p layer and vice versa). Therefore with the changing of the current direction time  $t_{r0}$  should be known to "clear" the layers. At this time the voltage across the diode is with the polarity correspondent to the direct conductivity, but this value is gradually decreasing and equal to zero at the end of the interval. During the further period of conductivity the current is decreasing and the voltage of the diode is close to the determined reverse biasing voltage of the source.

Fig. 1.3. Dynamics of the diode operation

The curve of the reverse current is characterised with such dynamic parameter as switch off charge  $Q_r$ . The more qualitative is the diode, the lower are  $t_r$  and  $Q_r$ .  $t_r$  of a middle quality diode is about 5  $\mu$ s, that of excellent quality 1 -  $\mu$ s. As the diode does not perform the functions of single conductivity element during the turning off process, it is obvious that with the increasing of the source voltage frequency up to some particular value the diode does not keep the function of reverse biasing more. If  $t_r = 5 \mu$ s, it takes place at 5  $\mu$ s of the period or 10  $\mu$ s of that. The acceptable frequency is

$$f_{\text{max}} = \frac{10^6}{10} = 100 \text{ kHz} . \tag{1-6}$$

As p-n junction is the base of all semiconductor devices they all have similar static and dynamic characteristics, i.e. a semiconductor element is not an ideal conductor and not absolutely high-performance.

$$t_r = \sqrt{\frac{Q \cdot 0.2}{500 \cdot 10^3}} = 6.32 \,\mu s \ . \tag{1-7}$$

Amplitude of the reverse current

$$I_{VRm} = \frac{500 \cdot 6,32 \cdot 10^3}{10^6 \cdot 0.1} = 31,6A . \tag{1-8}$$

Maximum available rated current of the modern produced diodes is kilo-amperes and rated voltage is higher than 10kV. For the decreasing of the power losses and the temperature of the structure more effective natural and forced cooling with air and liquid flows is provided.

### 1.2. Thyristors

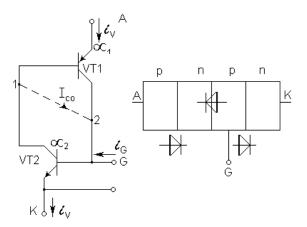

Thyristor is a controlled semiconductor switch with the features of a diode. Thyristor is formed with the specific connection of two transistors (Fig.1.4). VT1 transistor is of p-n-p type with the current transfer factor  $\alpha_1$ , and its collector forms the base of the second VT2 transistor that is simultaneously the control electrode (gate) G of the thyristor.

The base of the first transistor in its turn is connected with the collector of the second transistor. If the thyristor is supplied with direct voltage (positive pole to anode A, negative to cathode K) then the four-layer p-n-p-n structure of the thyristor (Fig.1.4) consists of two diodes of direct bias and one, that in the middle, is supplied with the reverse voltage. This diode conducts leakage current I<sub>CO</sub> formed from its minority charges flow.

Fig. 1.4. The equivalent circuit of the thyristor and four-layers structure

First of all the case when the control current  $i_G=0$  is under the reviewing. The collector current of transistor VT2 is equal to  $\alpha_2 i_V$ . The base current of transistor VT1 is  $i_V(1-\alpha_1)$ . Therefore for junction 1 of the circuit taking into account leakage current  $I_{CO}$  the following current equation is valid

$$i_V(1-\alpha_1) = I_{C0} + \alpha_2 i_V$$

(1-9)

Then the thyristor current

$$i_{v} = \frac{I_{C0}}{1 - \alpha_{1} - \alpha_{2}} \quad . \tag{1-10}$$

As it is known  $\alpha$  is zero with low emitter current of the thyristor structure. This feature provides the stability of the thyristor structure with low leakage currents. With the leakage current achieving a particular value (for powerful thyristors 30...50 mA)  $\alpha_1$  and  $\alpha_2$  are increased causing iv increasing and further increasing of  $\alpha_1$  and  $\alpha_2$ , etc., i.e., and avalanchelike switching-on process takes place. After this process  $(\alpha_1 + \alpha_2) > 1$  and the leakage current I<sub>CO</sub> changes its sign.

The leakage current can increase if

- 1) the voltage across anode and cathode is increasing,

- 2) the temperature of the structure is increasing,

- 3) the central junction is affected with an outside luminous flux,

- 4) the central junction is affected with an outside radiation flux.

The first opportunity is applied for the production of low-power diode with voltage switching or dinistor. The third opportunity to increase I<sub>CO</sub> to a necessary value by means of light is applied for the production of optical controlled thyristors.

Temperature is not used for the thyristor switching on, but during the utilization the increasing of the thyristor temperature should be taken into account. Therefore during the operation the voltage, at which the leakage current achieves its critical value, is increasing. The utmost temperature until which the thyristor can stand the direct voltage without additional control is assumed of  $120^{\circ}$ C.

The second case of the thyristor operation is when  $i_G > 0$ . Taking into account that the current of VT2 emitter is  $(i_V + i_G)$  the equation is

$$I_{CO} + \alpha_1 i_V + i_G = (1 - \alpha_2) (i_V + i_G).$$

(1-11)

Therefore

$$i_{v} = \frac{I_{C0} + \alpha_{2}i_{G}}{1 - \alpha_{1} - \alpha_{2}} \quad . \tag{1-12}$$

As it is obvious the increasing of the current factor and thyristor switching on can be achieved increasing the base current of transistor VT2 above its critical value. The control signal is short-time (30...100  $\mu$ s). The ratings of thyristor contain necessary control current and voltage. Typically the control current does not exceed 1 A, and the voltage - 4 V.

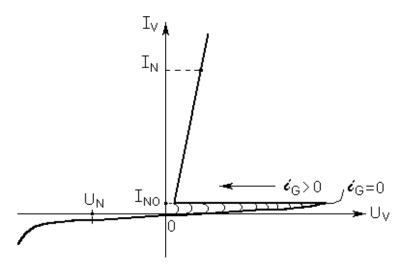

The volt-ampere characteristic of thyristor in on condition is similar to that of the diode (fig.1.5). But the threshold voltage can achieve  $U_0 = 1,2 \dots 1.3 \text{ V}$ . It should be taken into account that the VAC of on condition of the direct bias does not go from zero, but starts from comparatively low hold current  $I_{NO}$ . If the resistance of the circuit does not provide the current higher than  $I_{NO}$  the thyristor in this case will not be switched on.

Fig. 1.5. Volt-ampere characteristic of thyristor

While  $i_G = 0$  the characteristic of the direct bias is symmetrical to that of the reverse bias, i.e.  $i_V (U_V) = -i_V (-U_V)$ . When the level of threshold voltage is achieved in the direct bias the thyristor is on and VS characteristic stepwise transforms to the characteristic of the on-state with low direct voltage level.

In the 80th fully controlled thyristors were produced - so called Gate Turn Off thyristors. As in on-state  $(\alpha_1 + \alpha_2) > 1$  then for the conducting of basic current  $i_V$  (assuming that the leakage current  $I_{CO}$  is already decreased till zero) the following control current should be supplied

$$i_G = \frac{(1 - \alpha_1 - \alpha_2)i_V}{\alpha_2} < 0 \quad , \tag{1-13}$$

that can be about 30...70 % of basic current i<sub>V</sub>. If in on-state i<sub>V</sub> =200A,  $\alpha_1 = \alpha_2 = 0.7$  then

current of

$$i_G = \frac{-0.4.200}{0.7} = -114$$

A is necessary for switching on.

Although the time necessary for the flow of control current is small (about 5  $\mu$ s) the strength of the control electrode circuit should be increased as well as the circuit of high control current is necessary. Usually the capacitor discharge is applied.

The dynamic regimes are of great importance for all the thyristor types semiconductor elements: the processes of switching on, off, stability to fast changes of voltage.

The process of switching on is characterised with the gradual conductance of the structure in the direction from control electrode with speed 0.5 mm/µs. If the current of the basic circuit instantly flows through the initially small switching zone then high current density is produced there causing high losses and increased temperature. The temperature exceeding an acceptable one causes an irreversible damage of the structure.

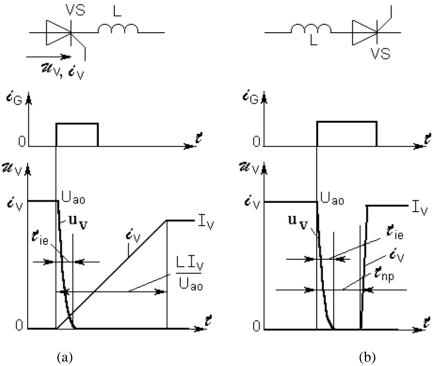

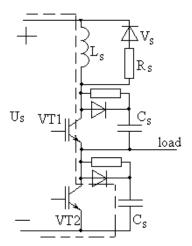

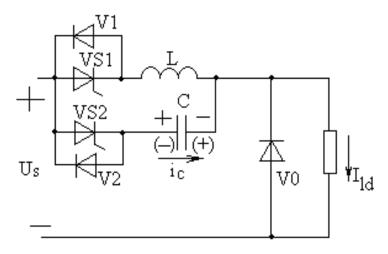

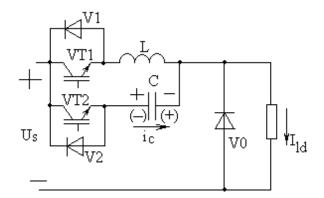

Therefore regular thermal regime of the initial switching zone requires the limitation of fast increasing of the current during the time of full switching on of the structure, for the modern thyristors this time is about 5...7 µs. There are two approaches to realise these requirements: by means of linear reactor and saturation reactor.

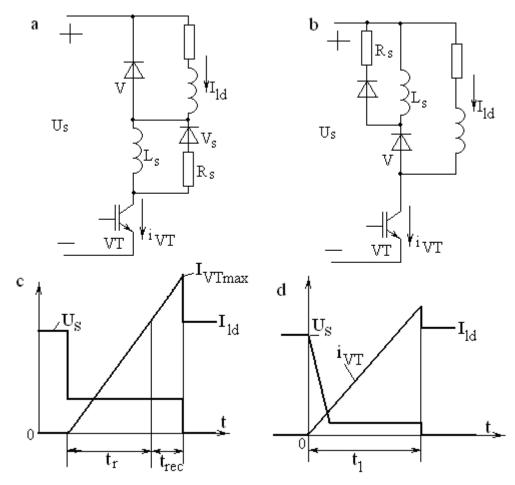

Fig. 1.6. The process of the thyristor switching with linear reactor (a) and saturation reactor (b)

The first variant applies the ratings of acceptable speed of current increasing [di / dt], and the inductance of the reactor connected in series with the thyristor (Fig.1.6.(a)) is calculated taking into account the level of the voltage just before switching on of the element  $U_{a0}$ :

$$L \ge \frac{U_{a0}}{\left[di/dt\right]} \tag{1-14}$$

Then the maximum losses of power during the switching on process tie are

$$\Delta P_{mie} \approx 0.25 U_{a0}^2 \frac{t_{ie}}{I} \quad , \tag{1-15}$$

but those average within the period T = 1 / f

$$\Delta P_{ievid} \approx 0.16 f \frac{U_{a0}^2 t_{ie}}{I} \quad . \tag{1-16}$$

As it is obvious from the expressions the power losses existing during the switching process are sharply increasing with the increasing of the throttle inductance. However this inductance is high enough and causes the voltage drop when the current of the basic circuit is changed in the quasi-steady process. Therefore instead of that linear the saturation reactor with square-form magnetizing characteristics of its core is often.

Until the core is not saturated the inductive resistance of the coil is almost infinite and there is no current in the circuit. The parameters of the throttle should be selected in terms of the fact that the time of operation in a non-saturated regime after supplying the thyristor with control signal should not be lower than  $t_{ie}$ :

$$t_{np} = \frac{(B_p - B_0)sw}{U_{a0}} \ge t_{ie} \quad , \tag{1-17}$$

where  $B_p$ ,  $B_0$  are the saturation and residual inductances (T) of the magnetic material, s, w - are the cross-section area (m<sup>2</sup>) and number of turns of the coil. As soon as the core is saturated and its inductive resistance is close to zero the structure of the thyristor is on and the increasing of the current does not cause the switching losses.

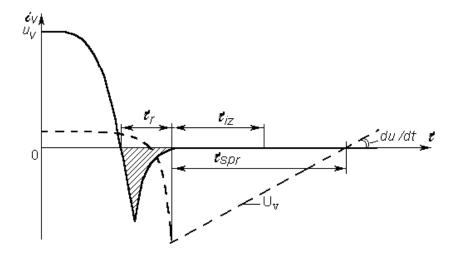

The other dynamic process is thyristor's switching off (Fig.1.7). Similar to the diode (Fig.1.3) after reaching zero level the current of the thyristor continues to flow in the reverse direction for some time and then in  $t_{r0}$  time the structure is recovered. At the end of this stage the reverse biasing value of the thyristor voltage is increasing. At this moment the changing of its polarity to the direct polarity (Fig.1.7) can cause the problem of the repeating thyristor switching on, i.e. an emergency situation. This is related to the fact that during the recovery process not all the majority charges of the thyristor structure return to the positions necessary for the direct bias voltage maintaining. That is why the reverse biasing voltage should correspond to the known time given in the thyristor ratings - off time  $t_{iz}$ .

Fig. 1.7. The diagram of the regular switching off process of thyristor

The process of switching off demonstrated in the diagram is successful as the duration time of the reverse biasing voltage is  $t_{spr} > t_{iz}$ . In the case of AC circuit  $t_{iz}$  limits the maximum thyristor operation frequency. Thus the half-period of the voltage should be longer than  $t_{iz}$  and

$$f_{\text{max}} < \frac{1}{2t_{i_r}}$$

(1-18)

If  $t_{iz} = 100 \mu s$  (weak thyristor), therefore  $f_{max} < 5 \text{ kHz}$ . The qualitative thyristors have  $t_{iz} = 20...30 \mu s$ , and can operate with frequency 15...25 kHz.

The off time of the thyristors has a special importance for the commutated DC circuits where the thyristor switching off is realised with the help of forced commutation with in advance charged capacitor. The higher is  $t_{iz}$ , the higher is the capacity necessary for the similar conditions. For the decreasing of the sizes of the commutation circuit the thyristors with low  $t_{iz}$  are applied.

The third dynamic process - increasing of the direct voltage - is connected with the thyristor direct voltage recovery speed after the off process. The middle junction (fig.1.4) with its direct bias has a particular capacity  $C_{np}$ . With fast recovered voltage the leakage current through this junction-capacitor is increased:

$$i_{C0} = i_{Cnp} = C_{np} \frac{du}{dt}$$

(1-19)

If du / dt is high current  $i_{C0}$  can exceed a critical value when transfer factors  $\alpha_1$  and  $\alpha_2$  of the thyristor equivalent transistors start increasing from the initial zero values. In this case the thyristor can be spontaneously switched on and cause an emergency situation. If critical current  $I_{C0} = 30$  mA, the junction capacity  $C_{np} = 100$ .  $10^{-12}$  F, then the critical value du / dt is 300 V/  $\mu s$ . For the safe switching of the thyristor the direct voltage should be supplied at time moment  $t_{spr}$  when the off processes of the thyristor are fully completed, i.e.  $t_{spr} > t_{iz}$  (Fig.1.7).

Basically the thyristors are produced for high enough powerful devices. Nowadays the thyristors are with rated currents up to some kA, rated voltage above 10kV, admissible [di / dt]>  $1000A/\mu s$ , [du / dt] >  $1000\ V$  /  $\mu s$  and off time lower than  $20\ \mu s$ .

#### 1.3. Transistors

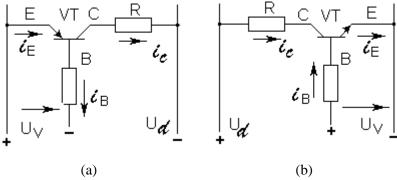

Bipolar transistor consists of 3 semiconductor layers: two p and one n, forming p-n-p transistor (Fig.1.8) and two n and one p forming n-p-n. One border layer and its electrode are called emitter (E) and signed with an array defining the direction of the current conducting (the current flows from the source positive pole to the negative). The layer in the middle together with emitter forms controlling bipolar junction or diode in the direction of the array and is called a base (B). The third layer with the help of outside voltage source carries a part of the emitter major charges getting the base layer because of the control voltage to the operation circuit. This layer is called a collector (C) (Fig.1.8).

The direction of the transistor array defines the necessary polarity of the control and operation voltage source: E of p-n-p transistor is connected to the positive pole directly or through resistor, B and C - to the negative pole of the control and operation voltage sources correspondingly (Fig.1.8.a); the electrodes of n-p-n transistor are connected to the sources in the opposite way (Fig.1.8.b).

To provide the transistor effect - carrying a part of the emitter major charges from base layer to the operation circuit - the voltage of the basic operation circuit should be higher than that of the control circuit  $U_{EB}$  or  $U_{BE}$ . The displayed circuits respond to so called common emitter circuit widely applied in the power converters.

In accordance with the Kirhhoff's Law the currents in the transistor circuit are

$$i_C = i_E - i_B \quad , \tag{1-20}$$

where all the currents can be with positive signs only.

The correlation of collector and emitter currents is called the factor of current conducting

$$\alpha = \frac{i_C}{i_E} < 1 \quad , \tag{1-21}$$

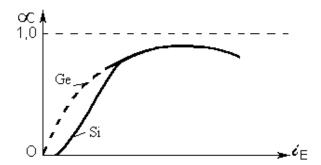

defining how effectively the major charges of the emitter are carried to the collector circuit. Relation  $\alpha = f(i_E)$  is of top importance for the forming of a complex p-n structure (Fig.1.9). Silicium has some dead zone at low emitter currents but then  $\alpha$  is increasing achieving its maximum at about a half of the rated current.

Fig. 1.8. p-n-p (a) and n-p-n (b) transistors connection

Fig. 1.9. Dependence of the Silicium and Germanium (Ge) transistors currents transfer factors on the emitter current

The relation of collector and base currents is a static factor of the current amplification  $\beta$ :

$$\beta = \frac{i_C}{i_B} = \frac{\alpha}{1 - \alpha} \quad . \tag{1-22}$$

As  $\alpha$  is a function of  $i_E$ , then  $\beta$  depends on  $i_E$ . The amplification of the current reaches its maximum value at  $\alpha_{max}$ . For example, if  $\alpha_{max}=0.95$ , then  $\beta_{max}=19$ . For the qualitative bipolar transistors  $\beta$  reaches 100 and more. However the regulation of high collector currents requires a high base current that complicates the application of BT.

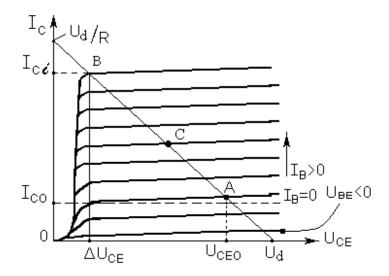

The operation of BT can be characterised with the help of collector current  $I_C$  dependence on the voltage collector-emitter  $U_{CE}$  (for n-p-n transistor) changing values of the base current (Fig.1.10). With a constant base current and increasing collector voltage the current of the collector sharply increases at the beginning, but later is almost constant. If the base current is zero the collector voltage is about 85% of the operation circuit voltage, and a low collector current is flowing (point A). Even if the current is low the voltage can be high enough with appreciable power losses. For example, is  $I_{CO} = 10$  mA, but  $U_{CEO} = 400$  V, then  $\Delta P_0 = 4$  W, that is high enough for the transistor. For better BT switching off the polarity of the control voltage is changed allowing decreasing of power losses to minimum.

Fig. 1.10. Collector current of n-p-n BT depending on collector voltage

The increasing of base current maintaining  $U_d$  unchangeable the collector voltage is decreasing and with high enough  $I_B$  the transistor is fully on, and the collector current is a bit lower than short circuit current  $U_d$  / R. It is called "saturation" of the transistor in operation regime, point B. The direct voltage  $\Delta U_{CE}$  in this regime can be lower than that of base-emitter, pointing that the collector-base diode is in the direct bias, i.e. the collector layer contains a lot of negative emitter charge carriers, but the base has a lot of positive and the diode conducts in the direction from base to collector (n-p-n transistor).

The power losses of the transistor in the saturated regime are not high. If  $U_d$  = 100 V,  $\Delta U_{CE}$  = 2 V, R = 10  $\Omega$ , the collector current is 9,8 A, but the losses in the transistor  $\Delta P_i$  = 19,6 W. If the transistor is operating at point C (Fig.1.10.) with  $U_{CE}$  =0,5  $U_d$ , then the current is 5 A, but the losses - 250 W.

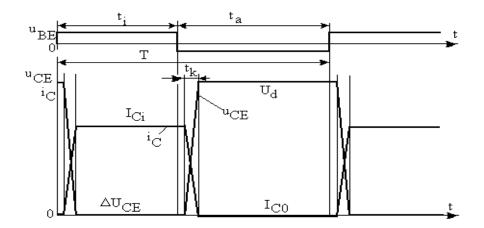

Taking into account low values of the losses in two regimes - saturated and off-state - the regulating effect in the power electronic systems is achieved with the application of these two regimes only: the transistor is operating in so called "switch" mode (Fig.1.11.). The losses within the operation period consist of those in the border regimes  $\Delta P_0$  and  $\Delta P_i$  and losses  $\Delta P_k$  of the transient periods from one state to other. If the transistor operates with a resistive load and both switching periods are the same then

$$\Delta P = \Delta P_0 + \Delta P_i + 2\Delta P_k = I_{C0} U_d \frac{t_a}{T} + I_{Ci} \Delta U_{CE} \frac{t_i}{T} + 2 \frac{I_{Ci} U_d t_k}{6T} \quad . \tag{1-23}$$

$I_{C0}$  and  $I_{Ci}$  are the collector currents in on and off states;  $t_k$  - switching time (typically 1...2  $\mu s$ );  $t_a$ ,  $t_i$ , T - the duration of the control signal in the on and off part of the switching period T (Fig.1.11.).

Fig. 1.11. Voltage and current diagrams of the transistor in "switch" mode with active load

With the increasing of frequency the specific switching time during the shortened period T is increasing, and the third component of losses is also growing - the specific commutation losses  $\Delta P_k$ . When the frequency is tens of kilohertz the commutation losses can achieve 50...70% of the admissible power losses of the transistors  $\Delta P_{TR}$ . For the calculation of the heating process expression (1-4) can be applied.

The ratings of transistors contain maximum admissible collector voltage in off state, maximum admissible current in on state, amplification factor as a function of  $I_C$ , voltage  $\Delta U_{CE}$  at  $I_{Cmax}$ , switching time and others.

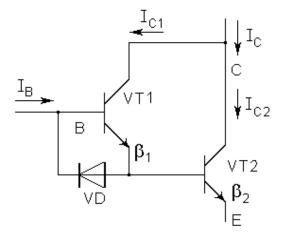

The most important disadvantage of bipolar transistors is a low amplification factor as well as dependence of power losses on the base current. In order to improve the static amplification factor the complicated transistor schemes are applied. In the case of two transistors connection it is called Darlington scheme (Fig.1.12).

Fig. 1.12. Darlington scheme

In this scheme the emitter current of the first transistor VT1 is the base current of the second one VT2:

$$II_{B2} = I_B + I_{C1} = I_B (1 + \beta_1).$$

(1-24)

The common collector current

$$I_C = I_{C1} + I_{C2} = \beta_1 I_B + \beta_2 I_{B2}$$

(1-25)

Taking into account (1-21) the static amplification factor of the scheme

$$\beta = \frac{I_C}{I_B} = \beta_1 + \beta_2 + \beta_1 \beta_2 \quad . \tag{1-26}$$

As it is obvious the common  $\beta$  is higher than the multiplication of amplification factors of the both transistors.

The second disadvantage of the transistors is their limited overload durability. If with constant base current in on state the collector current is increasing above some calculated value, i.e. in Fig.1.10. the line is turned clock wise, the collector current and power losses are growing. It can result in overheating of the structure and damage of the junctions. An operative control with the switching base signal can provide an avoidance of this situation. While the collector voltage is increasing the control signal should be switched off.

Modern bipolar transistors are produced for hundreds amperes of collector current and hundreds volts of collector voltage.

#### 1.3.1. Powerful Field Effect Transistors

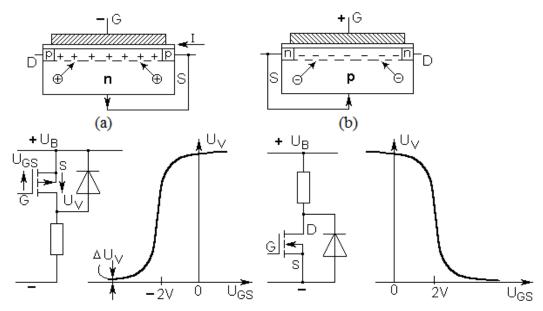

The other version of the transistors realisation is connected with the forming of current conducting channel by an outside electric field influence. Thus the MOSFET version has been realised. A channel can be formed by n carriers as well as p carriers forming correspondingly n channel or p channel field transistors.

Field transistors are formed on the basis of n or p layer adding at its edges contact areas of opposite conductivity. The sizes of this area define the thickness of conducting channel.

An insulating oxide layer is placed over this base but over this layer in its turn - a metal electrode G - a gate that is supplied with one pole of the control voltage. The other pole of the control voltage is supplied to the base, that in its turn is connected to one of the contact areas of the semiconductor - source (S). The second area is called a drain (D).

If the base is of n-conductivity type then the electrical field between G and S fills in the channel with p base minority carriers forming p channel. With this aim the gate should be supplied with voltage potential more negative than that of the base. As the base is connected to the positive contact area S then for the switching p channel transistor on gate G should be supplied from the negative electrode of the control voltage. The array of the base defines the polarity of the control electric field necessary for the switching on. As the gate is insulated from the base the control current is zero. If the base is of p-conductivity type, contact areas of n-conductivity, then the control electrical field between G and S can fill in the channel with n base minority charge carriers forming n channel. With this aim G should be connected to the positive potential but the base - to the negative contact area S. The scheme in Fig.1.13 demonstrates field effect transistor the gate G of which is connected to the positive control voltage electrode.

This transistor without control voltage normally is off, but with a necessary control voltage (typically less than 20 V) the channel is filled being called an enhancement mode MOSFET. The transistors are usually produced with an integrated fast-acting diode protecting from breakdown voltages. The switching on of the MOSFET requires about 4...7 V across G and S

(the threshold voltage is about 2...4 V). In fully on state the voltage across the transistor depends on the relation of the channel resistance and general load and channel resistance multiplied with the supply voltage. If the supply voltage is increasing then  $U_V$  across the switched on field transistor is also increasing. Together with it the transistor losses are also increasing. This is the most important disadvantage of the MOSFET elements.

In the informative materials the resistance of the channel  $R_{DS(on)}$  is defined, for example, for a 10 A MOSFET with rated voltage 100 V of about 0,1  $\Omega$ , with 200 V - 0,2  $\Omega$ , with 400 V - 0,6  $\Omega$ , with 1000 V - 1,2  $\Omega$ . Approximately

$$R_{DS(on)} = k \cdot U_{N^{1.5}}. (1-27)$$

If the admissible power losses in the element are 300 W (close to the typical parameters of powerful MOSFET) with voltage 1000 V the rated current can not exceed 15 A. It should be noted that MOSFET transistors can operate with the temperature of the structure up to  $150^{\circ}$ C.

Fig. 1.13. MOSFET with p channel conductivity (a) and n channel conductivity (b)

MOSFET transistors are very fast-operating, and their switching time is measured in nanoseconds. Typically on time is 20...50 ns, but off time - 200...250 ns. The switching time does not depend on the temperature. MOSFET can operate with the frequency up to several millions hertz.

MOSFET can operate in parallel connection, as its particular resistances of the channel provide the smoothing of the currents between the transistors. This is a very important feature allowing a comparative easy way to improve the power of the installation.

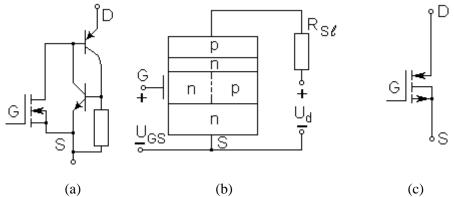

The MOSFET transistors under consideration are so called transistors of logic level L<sup>2</sup>FET. A new field effect transistor version is so called conductively modulated FET.

(COMFET). COMFET with n channel conductivity is in Fig.1.14 providing its equivalent scheme and structure.

Fig. 1.14. COMFET equivalent scheme (a), structure (b) and principal schematic symbol (c)

It is obvious that COMFET is a thyristor controlled with a field effect transistor. Therefore in on-state it is described with the volt-ampere characteristic with the direct voltage 2.5 V not depending on current. But the switching time is much higher than that of MOSFET. Typically their on time is 200 ns, but off time - 700...900 ns.

Taking into account that the voltage of COMFET in on-state does not depend on the operation voltage the rated voltages of COMFET with high enough currents (50...100A) can be increased to 1 kV and above.

#### 1.3.2. Bipolar transistors with insulated base (IGBT)

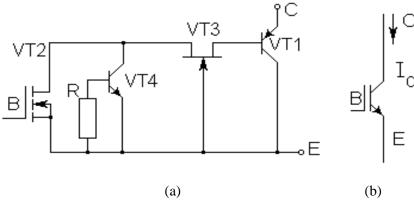

The integration of MOSFET transistor, bipolar transistor and at some rate thyristor in one element forms a switch called a bipolar transistor with insulated base with zero static control current, high rated voltage and current and small switching time (IGBT).

The equivalent scheme of IGBT is given in Fig.1.15 and resembles a pseudo-Darlington connection from p-n-p bipolar transistor VT1 and n-channel control field effect transistor VT2. A traditional field transistor VT3 connected between VT2 drain and VT1 base takes a part of direct voltage across the p-n-p transistor emitter (IGBT collector) and collector allowing to VT2 form some  $R_{DS(ON)}$  with a low voltage.

If the potential of the base is more positive than that of the emitter then with direct voltage VT2 and VT1 are on. In on-state the direct voltage can never be lower than that across p-n-p transistor diodes between emitter and base. The typical IGBT volt-ampere characteristics are in Fig.1.16.

The admissible temperature of this element is about  $+150^{\circ}$ C. As it is obvious the current in the circuit depends on the control voltage. For full switching on with low voltage drop (below 2V) a comparatively high control voltage should be supplied - close to maximum admissible 20V. The control voltage for switching off is minus 20 V.

Fig. 1.15. IGBT equivalent scheme (a) and schematic symbol (b)

When p-n-p transistor is switching on it is not in fully saturated condition as it disturbs VT1 base current flow. Therefore IGBT switching off is fast enough - from 100 to 3000 ns. If the off time is fast the switching losses are comparatively low that results in the opportunity to operate with high frequency.

IGBT are divided into 3 groups:

- S IGBT of standard operation speed with full on-time about 25 ns, full off-time 1600 ns, switching process power losses within the period 7.0 mJ (at rated current 10 A), that can operate with switching frequency till 1 kHz;

- F fast IGBT with full on-time about 13 ns, full off-time 600 ns, switching process power losses within the period 1.8 mJ (at rated current 10 A), that can operate with switching frequency till 10 kHz;

- U very fast IGBT with full off-time 190 ns, switching process power losses within the period 1 mJ, that can operate with switching frequency up to some tens kilohertz.

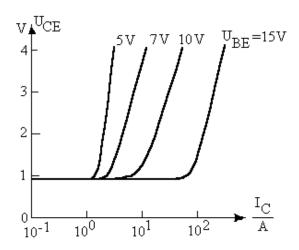

The switching power losses are reflected in the scheme in Fig.1.17 where once for short moment VT1, VT2 are on taking current  $I_C$  in throttle L that after the transistor switching on is conducted through diode V1 and stabiliser V2 forming initial and final collector voltage across the transistor under investigation.

When transistor VT3 is on its switching process takes place with the voltage of stabiliser UC when its current is growing from 0 to  $I_C$ , but then with full  $I_C$  the voltage is decreasing from  $U_C$  to zero. For some period while switching off the collector current is equal to  $I_C$ , the collector voltage is growing, but after the stabiliser is on  $U_C$  is constant and the current is decreasing. The periods of time presented in the figure are related to TGBTs of F group. If within the considered experiment  $U_C = 450$  V,  $I_C = 10$  A, then the common power losses are

$$\Delta~E_k = (450.~5 + 225.~10)~(15 + 600)$$

.  $10^{\text{-9}} = 2{,}77~\text{mJ}.$

Fig. 1.16. Characteristics of an IGBT transistor at different U<sub>BE</sub> values

IGBT structure is p-n-p-n junction therefore it is similar to that of thyristor. If the sum of the transfer factors of the VT1 and VT2 currents is equal to 1 then the structure spontaneously switches on. That can take place at the sharp direct voltage increasing speed du/dt.

Fig. 1.17. Investigation of IGBT switching: scheme (a), diagrams of the current and voltage during the process of switching (b)

IGBT long operating currents achieve some hundreds amperes, but admissible direct voltages - up to 2-3 kV.

#### 1.4. Power losses

The temperature of a semiconductor element determines its power losses and the parameters of its cooling system. In steady-state regime the steady temperature is

$$\Theta_p = \Theta_0 + \Delta P_p . R_T \quad , \tag{1-28}$$

where  $\Theta_0$  is the temperature of the environment,  $\Delta P_p$  is the power losses in semiconductor (W),  $R_T$  - stationary thermal resistance of the cooling system ( ${}^0C/W$ ).

Power losses for the diodes and thyristors can be calculated in accordance with expression (1-3), but for the transistors operating in the mode of switching - in accordance with -

$$\Delta P_p = U_v J_v \cdot \gamma + \Delta E_k \cdot f \quad , \tag{1-29}$$

where  $U_v$ ,  $I_v$  are the voltage and current of the element in on-state,  $\Delta E_k$  - power losses within the switching process (J), f - switching frequency (Hz),  $\gamma$  - relative time of switching on within the switching period T=1/f.

If all the parameters and the admissible temperature of the structure are known  $[\Theta_p]$ , then maximum admissible switching frequency can be defined  $f_{max}$ . For example, if IGBT transistor temperature is  $[\Theta_p]{=}130^0C$ , environment temperature is  $30^0C$ ,  $R_T{=}3~^0C/W$ ,  $\gamma{=}0,5$ ,  $I_v{=}10~A$ ,  $U_v{=}2~V$ ,  $\Delta E_k=2,77~mJ$ , then the maximum admissible switching frequency is  $f_{max}{=}8~kHz$ .

This methodology of calculations of the heating regime can be applied also for the other semiconductor elements. The stationary thermal resistance depends on the construction of radiator as well as on the method of cooling (Fig.1.18). The best construction of a semiconductor is a pill form with double side radiator. If the semiconductor construction is cooled with an air flow with the speed of 12 m/s, then the stationary thermal resistance is two times lower if to compare it with the cooling under natural condition. In many cases the rated current of the semiconductors is given for the forced ventilation regime with speed 12 m/s.

An improved cooling can be realised also with a liquid flowing through the radiator. Usually in the case of rated cooling regime the speed of the liquid flow is 3 l/min.

In many cases it is necessary to calculate the heating of p-n structure for the short-time pulse-type current. If the duration of a current pulse flowing through the element is lower than that for the steady-state (usually for some hundreds seconds) then the values of transient thermal resistance  $r_T$  dependent on time is applied (Fig.1.18).

The calculation is made with the help of superposition principle according to the changes of the temperature during the time of each pulse and the following infinitely long pause: starting with each next pulse the value of positive power losses is acting; starting with each pause the value of positive and negative power losses is acting infinitely long, the values calculated during the pulse and pause are summed up.

Then after 1 pulse the temperature of the structure is

$$\Theta_1 = \Theta_0 + \Delta P.r_{T10} \quad , \tag{1-30}$$

after a pause -

$$\Theta_2 = \Theta_0 + \Delta P \cdot r_{720} - \Delta P \cdot r_{721} , \qquad (1-31)$$

after the second pulse -

$$\Theta_3 = \Theta_0 + \Delta P(r_{T30} + r_{T32} - r_{T21}) \quad , \tag{1-32}$$

after the second pause -

$$\Theta_4 = \Theta_0 + \Delta P(r_{T40} + r_{T42} - r_{T41} - r_{T43}) \tag{1-33}$$

etc., where  $r_{Tab}$  is a transient thermal resistance for the time interval  $t_a - t_b$ ;  $\Delta P - power$  losses within the current pulse.

If the number of the pulses is high the heating process is close to a stationary.

Fig. 1.18. Changes of the transient thermal resistance in time (a) and influence of the pulse type power losses onto the heating of the structure (b)

### 1.5. Comparison of Semiconductor Devices

Only a few definite statements can be made comparing all these semiconductor devices since a number of properties should be considered simultaneously and the devices are all the time evolving at a rapid pace [1]. The basic comparative parameters of semiconductor devices are given in Table 1-1, where  $U_{op}$  – is an operation voltage,  $I_{op}$  – current of operation, operation frequency -  $f_{op}$ .

| Table 1-1. The basic compar | rative parameters of | semiconductor devices |

|-----------------------------|----------------------|-----------------------|

|-----------------------------|----------------------|-----------------------|

|             | diodes         | thyristors     | BT                               | MOSFET                          | IGBT                            |

|-------------|----------------|----------------|----------------------------------|---------------------------------|---------------------------------|

| $ m U_{op}$ | 200V-<br>12kV  | 12kV           | 1700V                            | 4000V                           | 6500V                           |

| $I_{op}$    | 300A-<br>10kA  | 1000A-<br>6kA  | 120A                             | 2000A                           | 2400A                           |

| $f_{op}$    | 400Hz-<br>xMHz | 400Hz-<br>xkHz | x10kHz                           | 100kHz-<br>xMHz                 | x1100k<br>Hz                    |

| Control     | -              |                | With current, high control power | With voltage, low control power | With voltage, low control power |

Unlike BT the reverse voltage of MOSFET supplied to the gate of the transistor can achieve 30 V that significantly fasten the process of discharging of the number of minor charge carriers. MOSFETs as well as IGBTs have a high capacitance of the gate, recharging of which requires significant control currents. If to compare with BT the advantage of MOSFET is increased operation speed. Switching on time does not depend on the operation regime and is about 20...25ns with the delay not higher than 50ns. The time of switching off depends on relation of drain and source currents.

For decreasing of losses in the on-state the MOSFET is introduced into saturated regime with the supply of gate current. Therefore like in BT at the stage of switching on the process of minor charge carriers takes place. It results in the switching of delay and can be in the range from 20ns to  $5\mu s$ .

Besides the high characteristics of MOSFET, IGBTs are much more qualitative in their operation speed and control power. Their most important advantage is low resistance of p-n-barrier in on-state that is  $0,1...0,025\Omega$ .

The comparison of semiconductor devices demonstrates fast development of those during the last 20-25 years with a significant increasing of power – from some Watts to MW. The frequency range is very wide – from Hz to MHz. The similar increasing takes place with the maximum currents and voltages.

#### References:

[1] Mohan N., Undeland T., Robbins W. Power Electronics: Converters, Application, Design. – NY: John Wiley and sons, 1989, 667 pp.

# 2. Hard-Switching DC-DC Converters

### Ilja Galkins

Riga Technical University, Latvia

### 2.1. Fundamentals of Hard-Switching DC/DC Converters

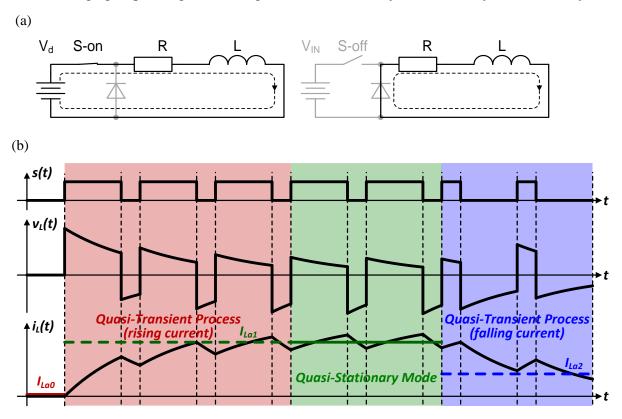

#### 2.1.1. Quasi-Stationary Mode

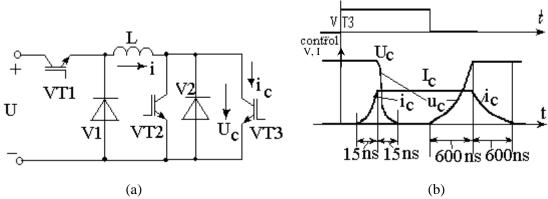

As it is follows from their name, the hard-switching DC/DC converters transform constant voltage of their input into another constant voltage of their output (or transform constant current into constant current). Such converters, in fact, continuously operate in one or another transient mode defined by particular combination of switches. In the same switching period there are several converter states and several transients (at least two). The exact analysis of these transients is too complicated and bulky. However, it is possible to split these transients into two large groups, irregular and regular, which are analyzed in more systematical way.

Fig. 2.1. Operation modes of switching converters: states of switching circuit (a) and operation diagrams (b)

The irregular transients are always different and form different values of system variables at the end of the new switching period. So while the irregular transients occur it is not possible to speak about repetitive processes – then the converter operates in the quasi-transient mode. In contrast, the regular transients repeat in each switching period and their fragments form periodical signals, i.e. then all variables are piece-wise periodical functions described by the following general equation:

$$x(t) = x(t + n \cdot T_{sw}), \qquad (2-1)$$

where: x(t) – is a variable (instantaneous voltage, current, power etc.), but n – integer number. The corresponding mode is called quasi-stationary or static or steady state. The quasi-stationary mode is the main subject of analysis of power electronic converter.

An example of the quasi-transient and quasi-stationary modes of operation of an electronic converter is shown in Fig. 2.1. In this example switching period consists of two stages: when the switch is on, Fig. 2.1.(a), and off, Fig. 2.1.(b). When the switch is on the load current is rising, when it is off – falling. In the quasi-stationary mode of operation this increase is equal to the following drop, so that the output current is the same at the beginning and at the end of the period (green area). Note that although the current is the same at the ends it is changing in the middle.

In the transient mode the increase and drop are different. If the difference is positive then the resulting process is uprising (red area), but if negative – the process is descending (blue area).

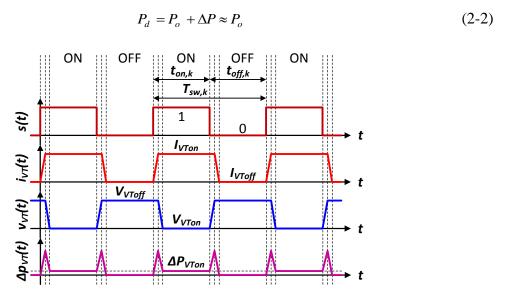

# **2.1.2. Operation of Semiconductor Elements in Hard-Switching Converters**

Semiconductor elements in the discussed converters operate in switching mode – i.e. are either completely "on" (conducting full operating current at low voltage drop) or completely "off" (endure full operation voltage at negligible leakage current) or toggling between one of the above two states (Fig. 2.2.). This operation is characterized with significant on-state and switching power losses  $\Delta P$  which, however, are much lower than the controlled power and are ignored in this chapter (see Chapter 1 for more details of switch operation). Therefore, the input power  $P_d$  of switching converters is approximately equal to their output power  $P_o$ :

Fig. 2.2. Operation of semiconductor elements in hard-switching converters

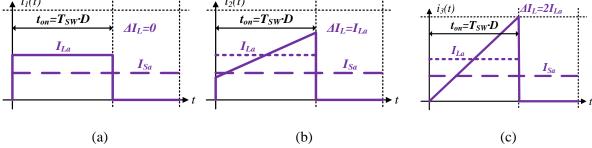

The switching times are typically negligible compared with switching period  $T_{sw}$ , so it is possible to say that switches are "on" or "off". Then for each switch it is possible to compose its switching function s(t), which values are either 1 (if the corresponding switch is "on") or 0 (if it is "off"). The definite integral of the switching function of a switch within its k-th operation cycle (switching period) produces the value, known as "duty cycle"  $D_k$ :

$$D_k = \frac{1}{T_{sw,k}} \int_{kT_{sw}-T_{sw}}^{kT_{sw}} s(t)dt = \frac{t_{on,k}}{T_{sw,k}},$$

(2-3)

where k is index – number of the switching cycle in their sequence since the beginning of the operation. Note that the  $D_k$  is rather function of this index, but not a time function (it is constant within the same switching cycle). Also it must be noted that the switching periods  $T_{sw,k}$  are usually constant – the corresponding control mean is called Pulse-Width Modulation (PWM).

The duty cycle  $D_k$  is defined by the control system and its dynamic (real-time) calculation is not a subject of this course. However, the static definition of this parameter is directly related to the operation of corresponding converters and is discussed below.

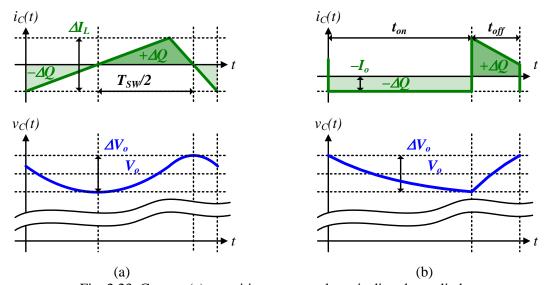

# 2.1.3. Operation of Inductors and Capacitors in Quasi-Stationary Mode

The capacitors and inductors play two roles in the hard-switching converters – they serve either as filtering elements or as energy transferring elements. These elements may also have the third function – sometimes they serve as an energy sources: the capacitors – as voltage sources, but the inductors – as current sources.

The voltage across filtering capacitors and the current in the filtering chokes is almost constant with exception of low ripples (defined as an input parameter of the design). Therefore the energy of filtering elements is also almost constant.

In contrast, the voltage across energy transferring capacitors and current in the energy transferring inductors may vary significantly within a switching cycle. Operation of many switching converters is based on energy transfer through such elements.

In spite of their function there are certain rules of capacitors and inductor operation in the quasi-stationary mode. Understanding of these rules helps to develop the equations of static operation of electronic converters.

The main operation rule for capacitors (C) follows from the voltage equilibrium at the ends of the switching period  $v(t)=v(t+T_{sw})$  then it is possible to compose the equation

$$\Delta v_C = v_C(t + T_{sw}) - v_C(t) = \frac{1}{C} \int_0^{T_{sw}} i_C(t) dt = \frac{T_{sw}}{C} \cdot \frac{1}{T_{sw}} \int_0^{T_{sw}} i_C(t) dt = \frac{T_{sw}}{C} \cdot I_{Ca} = 0, \qquad (2-4)$$

from which the main rule of capacitor follows – capacitor's average current in quasistationary mode is 0. In the similar way it is possible to prove that the average inductor's voltage in the quasi-stationary mode has also to be 0. Analytically it is written as

$$I_{Ca} = \frac{1}{T_{sw}} \int_{0}^{T_{sw}} i_C(t)dt = 0$$

and (2-5)

$$V_{La} = \frac{1}{T_{sw}} \int_{0}^{T_{sw}} v_L(t)dt = 0.$$

(2-6)

(2-5) and (2-6) themselves or (2-5) in conjunction with Kirchhoff's current law or (2-6) in conjunction with Kirchhoff's voltage law significantly simplify the calculation of other averaged parameters.

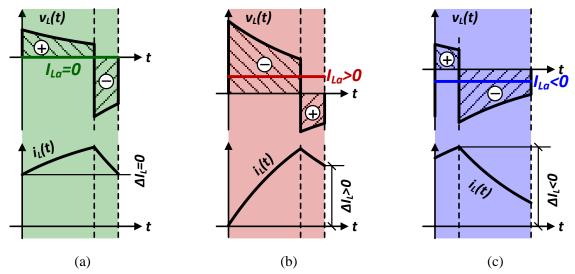

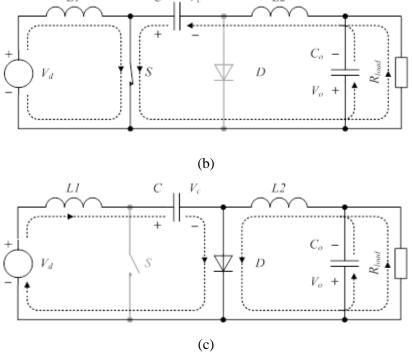

Fig. 2.3. Voltage balance across inductor: zero – final current is the same (a), positive – final current is higher (b), negative – final current is lower (c)

Fig. 2.3. reveals the details of the voltage balance across the inductor. Fig. 2.3.(a) presents the balanced inductor operation. In this case the square of the positive voltage pulse is equal to the square of negative. Therefore, the average value of the voltage is 0. In this case the current increase corresponding to the positive pulse is fully compensated by the current decrease caused by the negative. So, the inductor current at the beginning of the period is the same like at the end.

In contrast, in Fig. 2.3.(b) and Fig. 2.3.(c) unbalanced occasions are given. Fig. 2.3.(b) shows the occasion when the positive pulse is more valuable. Then the average voltage is positive, current increasing is more intensive and inductor's current at the end is higher. Fig. 2.3.(c) presents the case when the negative pulse is larger. It corresponds to the negative average voltage, weaker current increase and lower inductor's current at the end.

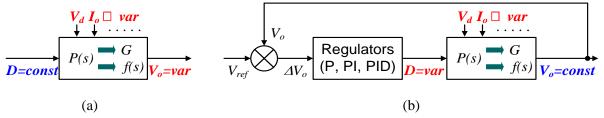

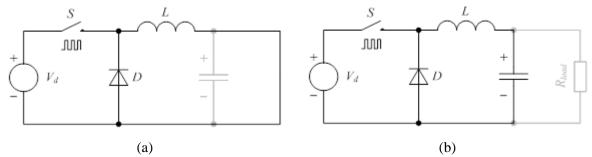

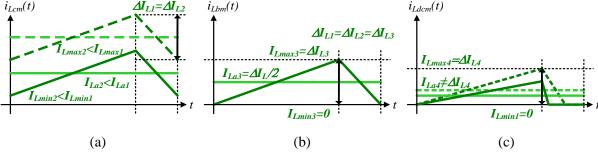

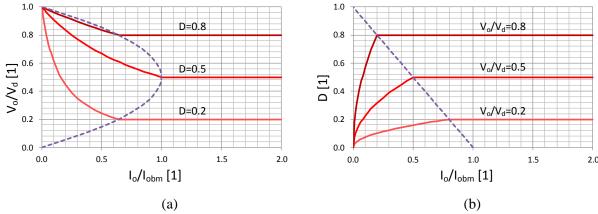

### 2.1.4. Open and Closed Loop Operation

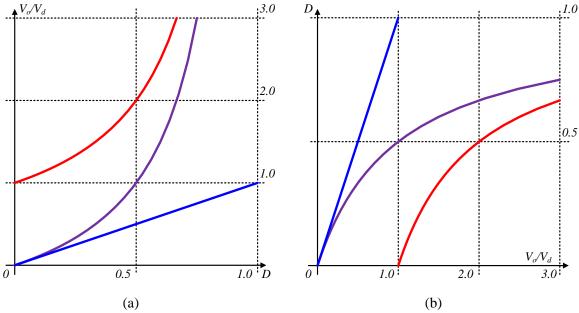

The logic and order of analysis of power converters depend a lot on the system configuration. If it is an open loop system – a system without feedbacks - shown in Fig. 2.4.(a), then the aim of the analysis is to find the reaction of the system on the parameter changes when the main regulation variable – duty cycle remains constant. In this case the output characteristic  $V_o$ =f(D) and load characteristic  $V_o$ =f(I<sub>o</sub>) are constructed and investigated.

Another occasion – is a closed-loop system with a voltage feedback, Fig. 2.4.(b). The output voltage in such systems is kept constant by means of the wise real-time modification of the duty cycle. Then the regulation characteristic  $D=f(V_d)$  and stabilization characteristic  $D=f(I_o)$  are analyzed.

Fig. 2.4. Open (a) and closed (b) loop configuration of DC/DC converters

# 2.1.5. Types of DC/DC Converters

It is possible to split the hard-switching DC/DC voltage converters in two groups: converters with energy transferring inductor (transformer) and converters = switching circuits + filters. The first group consists of such converters as classic buck (step-down), boost (step-up), buck/boost (step-up/step-down), Chuk, SEPIC and Zeta. The second group includes, for example, bridge and half-bridge circuits, as well as, again, buck converter. The following section of this chapter reveals the detail of operation of these converters.

# 2.2. DC/DC converters with energy transferring magnetic element

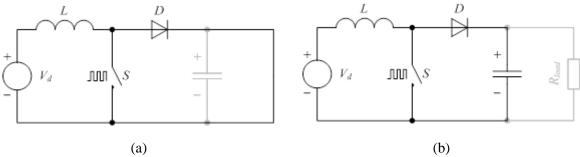

# 2.2.1. Genesis of basic DC/DC converters with energy transferring inductor

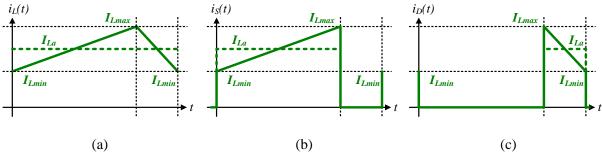

As it was shown in the previous section the average voltage across inductors in the quasistationary mode is 0. At the same time their current may vary in a wide range. If within some time period an inductor is connected to a positive voltage (direct current path) like in Fig. 2.3..(a), its current will rise from  $I_{Lmin}$  to  $I_{Lmax}$ , but its energy – as:

$$E_{L_{\min}} = \frac{L \cdot I_{L_{\min}}^2}{2} \Rightarrow E_{L_{\max}} = \frac{L \cdot I_{L_{\max}}^2}{2}.$$

(2-7)

Then it is possible to say that the inductor is charged from the positive voltage source. Then if the inductor is attached to a negative voltage (freewiling current path often provided by diodes), like in Fig. 2.3..(b), its current will drop from  $I_{Lmax}$  to  $I_{Lmin}$  and energy will decrease as

$$E_{L_{\text{max}}} = \frac{L \cdot I_{L_{\text{max}}}^2}{2} \Rightarrow E_{L_{\text{min}}} = \frac{L \cdot I_{L_{\text{min}}}^2}{2}.$$

(2-8)

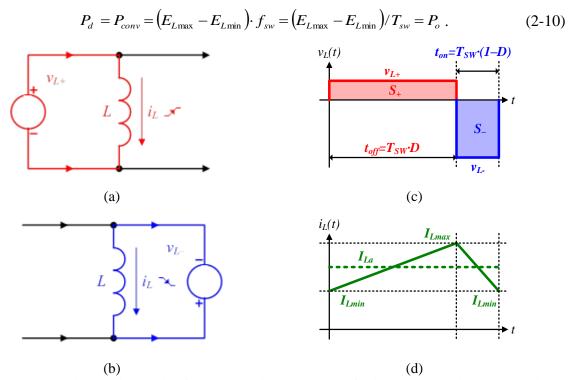

It means that the inductor is being discharged to the second voltage source. The difference of energy

$$\Delta E = E_{L_{\text{max}}} - E_{L_{\text{min}}} \tag{2-9}$$

is transferred from the first source (input) to the inductor during the first stage and from the inductor to the second source (output) during the second stage. This process is regarded here as energy transmission through the energy transferring inductor. Here the voltage across the inductor consists of positive and negative pulses of the same square, Fig. 2.3.(c), but the

current – is triangular, Fig. 2.3.(d). The converter power  $(P_{conv})$  depends on the commutation frequency and can be expressed as:

Fig. 2.5. Typical operation cycle of converter with energy transferring choke: positive voltage is applied (a), negative voltage is applied (b), operation voltage (c), operation current (d)

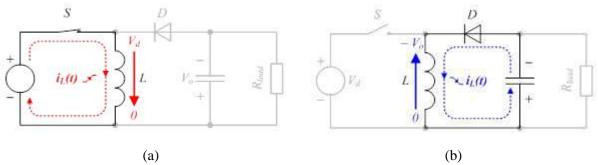

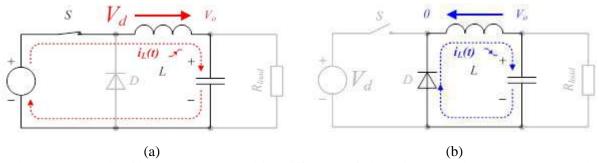

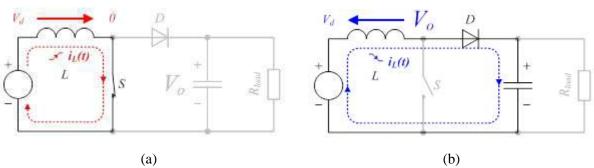

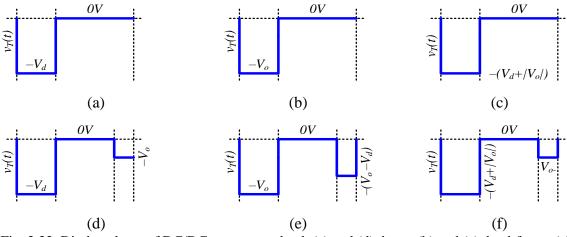

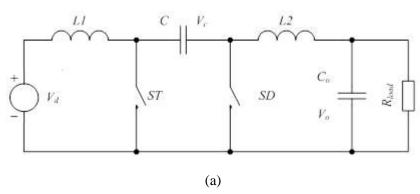

#### Applying input and output voltages directly

The direct implementation of the above described principle forms a switch mode converter known as inverting buck/boost (step-up/step-down). Since in this circuit the input voltage and output voltages are applied to the inductor one by one directly there is no theoretical limitation on their values — they may be equal or one of them may be higher — zero voltage balance can be achieved by means of the correct choice of pulse lengths (duty cycle). On the other hand the output voltage has to be negative.

This approach may be implemented also with positive output voltage. The positive input voltage can be applied as previously, red path in Fig. 2.7.(a). Then, since the second pulse across the inductor has to be negative, the positive output voltage has to be applied in reverse direction – blue path in Fig. 2.7.(a). Finally, grounds of two sources are connected - green wire in Fig. 2.7.(a). The obtained converter, known as non-inverting buck/boost, is given in Fig. 2.7.(b). Note that it has 2 switches in each current path. The forming of the direct current path is explained in Fig. 2.7.(c), but the configuration of the free wiling path is shown in Fig. 2.7.(d).

Fig. 2.6. Direct commutation of the input and output voltages – synthesis of inverting buck/boost converter: positive input voltage is directly applied (a), negative output voltage is directly applied (b)

Fig. 2.7. Direct commutation in non-inverting buck/boost converter: the input is applied directly (red) (a), the output – reversely (blue), grounds are connected (green), common view (the same colours) (b), positive input is directly applied (c), positive output is reversely applied (d)

#### Applying voltage differences

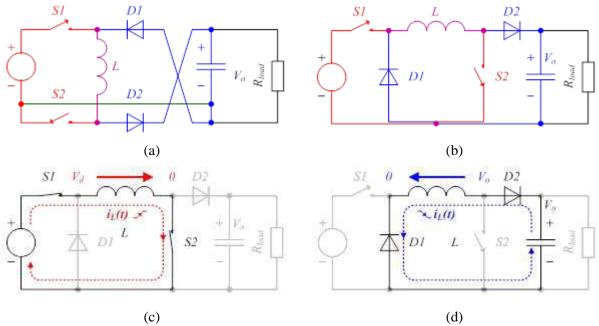

It is possible to form the voltage pulses across the inductor not only applying input/output voltages directly, but also utilizing voltage differences. This opportunity, however, is available only if the fact which of the voltages is higher is known. It is also important to provide (in average) the flowing-out current of the input source, as well as flowing-in current of the output source (otherwise the power is not transferred from the input to the output). If these conditions are fulfilled a circuit which applies the difference in correct direction can be synthesized utilizing a set of formal rules: 1) positive charging voltage pulse is applied through a couple of controllable switches; 2) negative discharging voltage pulse is applied through a couple of diodes; 3) parallel switches can be substituted with a short-circuit.

If the value of the input voltage is higher than those of the output, the difference of input and output voltages is positive, but of output and input – negative. One opportunity assumes obtaining the positive voltage pulse across the inductor (charging pulse) as a difference of input and lower output voltages – Fig. 2.8.(a). The current in such loop flows from the input source through the inductor to the output. The negative (discharging) voltage pulse can be

obtained as the output voltage applied in the reverse direction – Fig. 2.8. (b). Then it is possible to connect one terminal of the inductor to the lower output voltage, but the second – toggle between the input voltage and ground. The corresponding switching circuit is known as buck (step-down) converter due to its natural feature to decrease voltage. There are other combinations of such voltages (**Table 2-1**), but most of them are either the circuits already known or those that have reverse biased electronic switches on their input that makes the forward current flow impossible.

Fig. 2.8. Synthesis of buck converter: positive difference of higher input and lower output voltage is directly applied (a), positive output voltage is reversely applied (b)

| $v_{L+}$    | $v_{L-}$     | Remarks                                                                 |

|-------------|--------------|-------------------------------------------------------------------------|

| $V_d$       | $-(V_d-V_o)$ | Circuit with limited functionality                                      |

| $V_d$       | $-V_o$       | Non-inverting buck/boost converter                                      |

| $V_d - V_o$ | $-V_d$       | Circuit with limited functionality                                      |

| $V_d - V_o$ | $-V_o$       | Buck converter (Fig. 2.8)                                               |

| $V_o$       | $-V_d$       | Reversed non-inverting b/b converter – no forward current flow possible |

| $V_o$       | $-(V_d-V_o)$ | Reversed boost converter – no forward current flow possible             |

Table 2-1. Possible voltages across inductor if input voltage is higher

Fig. 2.9. Synthesis of boost converter: positive output voltage is directly applied (a), positive difference of higher output and lower input voltage is reversely applied (b)

Another occasion – the output voltage is higher than the input. Then the difference of input and output voltages is negative, but that of output and input – positive. One of the circuits with flowing-out input current is based on forming the positive voltage pulse across the inductor (charging pulse) applying the input voltage directly – Fig. 2.9.(a), but the negative pulse (discharging) – applying the difference of lower input and higher output voltages – Fig. 2.9.(b). Then the first terminal of the inductor can be connected to the input source, but the second – toggled between the output and ground. The obtained switch-mode converter given in Fig. 2.9 is known as boost or step-up, due to its feature to increase the voltage. Again, most

of the other combinations of voltages (**Table 2-2**) produce either known schematics or the converters that cannot operate.

| $v_{L+}$    | $v_{L-}$     | Remarks                                                                 |  |  |

|-------------|--------------|-------------------------------------------------------------------------|--|--|

| $V_d$       | $-(V_o-V_d)$ | Boost converter (Fig. 2.9.)                                             |  |  |

| $V_d$       | $-V_o$       | Non-inverting buck/boost converter                                      |  |  |

| $V_o - V_d$ | $-V_d$       | Reversed buck converter – no forward current flow possible              |  |  |

| $V_o - V_d$ | $-V_o$       | No forward current flow possible                                        |  |  |

| $V_o$       | $-V_d$       | Reversed non-inverting b/b converter – no forward current flow possible |  |  |

| $V_o$       | $-(V_o-V_d)$ | Circuit with limited functionality                                      |  |  |

Table 2-2. Possible voltages across inductor if input voltage is lower

# 2.2.2. Static operation of DC/DC converters with energy transferring inductor

Static operation of DC/DC converters is their operation in quasi-stationary mode. In this mode the instantaneous functions of converter's variables are periodical. This makes their description possible with the corresponding average values as well. At the same time, the most important element of these converters is their energy transferring inductor. That is why the average voltage and current equations for this inductor in fact describes the operation of the converter and are the most important during the analysis.

The main target during this analysis is the output voltage as a function of the duty cycle and output current. The other significant parameters of the discussed converters are output voltage, input current, voltages and currents of electronic switches, as well as those of the output capacitor.

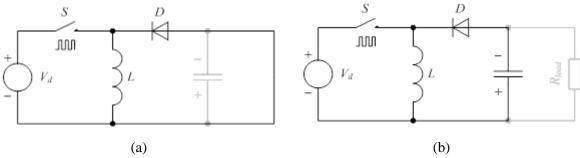

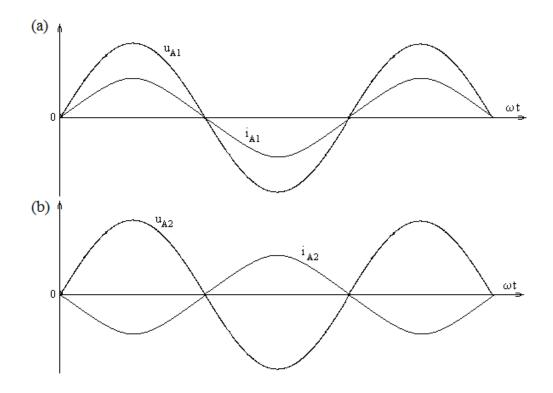

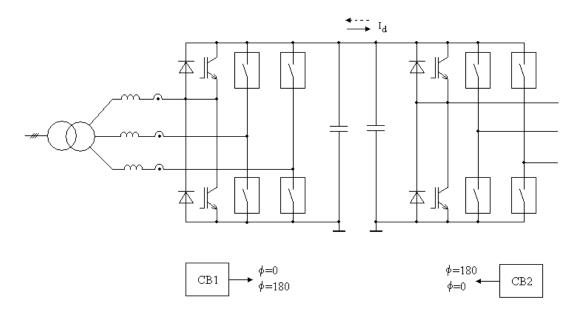

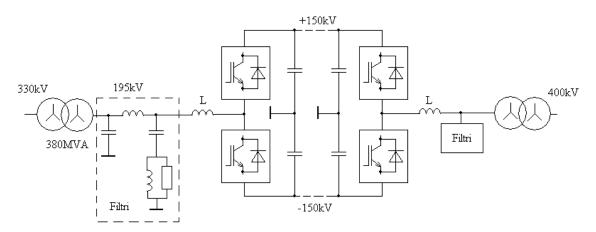

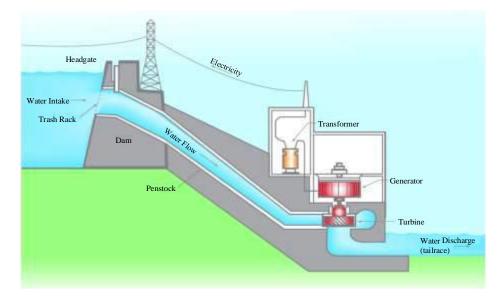

There are two basic modes of operation of the DC/DC converters with energy transferring inductor identified by the current pattern in the time domain: continuous conduction mode and discontinuous mode of the inductor current.