Jurandyr S. Nogueira

# Eletrônica Digital Básica

#### UNIVERSIDADE FEDERAL DA BAHIA

REITORA

Dora Leal Rosa

VICE REITOR Luis Rogério Bastos Leal

#### EDITORA DA UNIVERSIDADE FEDERAL DA BAHIA

DIRETORA Flávia Goulart Mota Garcia Rosa

#### CONSELHO EDITORIAL

Alberto Brum Novaes

Angelo Szaniecki Perret Serpa

Antônio Fernando Guerreiro de Freitas

Caiuby Alves da Costa

Charbel Ninõ El-Hani

Cleise Furtado Mendes

Dante Eustachio Lucchesi Ramacciotti

Evelina de Carvalho Sá Hoisel

José Teixeira Cavalcante Filho

Maria Vidal de Negreiros Camargo

# Eletrônica Digital Básica

Jurandyr S. Nogueira

© 2011, by Jurandyr Santos Nogueira. Direitos para esta edição cedidos à Edufba. Feito o depósito legal.

Capa e Arte final Amanda Santana da Silva

Normalização Adriana Caxiado

#### Sistema de Biblioteca da UFBA

Nogueira, Jurandyr Santos.

Eletrônica digital básica / Jurandyr Santos Nogueira. - Salvador: EDUFBA, 2011. 170 p.

ISBN 978-85-232-0836-3

1. Eletrônica digital. I. Título.

CDD - 621.3815

Editora filiada à

## **EDUFBA**

Rua Barão de Jeremoabo, s/n, Campus de Ondina,

40170-115 Salvador-BA Brasil

Tel/fax: (71)3283-6160/3283-6164 www.edufba.ufba.br | edufba@ufba.br

#### **SUMÁRIO**

# 1. INTRODUÇÃO AOS SISTEMAS NUMÉRICOS | 9

- 1. 1. CONVERSÃO ENTRE SISTEMAS NUMÉRICOS | 10

- 1. 1.1. Conversão de um Número numa Base qualquer para Decimal: $(N)_T \Rightarrow (N) \mid_{11}$

- 1. 1.2. Conversão de um Número Decimal para uma Base qualquer:  $(N)_{10} \Rightarrow (N)_{r+13}$

- 1. 1.3. Conversão de um Número numa Base  $r_1$  para a Base  $r_2$ :  $(N)r_1 \Rightarrow (N)r_{2+17}$

- 1. 1.4. Conversões entre Binário, Octal e Hexadecimal | 19

- 1. 2. CÓDIGOS BINÁRIOS | 23

- 1. 3. Exercícios I | 25

# 2. INTRODUÇÃO À ÁLGEBRA BOOLEANA | 27

- 2. 1. OPERADORES DA ÁLGEBRA BOOLEANA | 28

- 2. 2. CIRCUITOS EQUIVALENTES E SIMBOLOGIA C.I.'S | 30

- 2. 3. POSTULADOS E TEOREMAS DA ÁLGEBRA BOOLEANA | 34

- 2. 4. PROPRIEDADES DAS FUNÇÕES "NAND" | 43

- 2. 4.1. Expressões que envolvem apenas "NAND's". / 44

- 2. 5. PROPRIEDADES DAS FUNÇÕES "NOR" | 44

- 2.5.1 Expressões que envolvem apenas "NOR's / 45

- 2. 6. PROPRIEDADES DAS FUNÇÕES "XOR" E "XNOR" | 46

- 2. 7. FORMAS CANÔNICAS | 47

- 2.7.1 Funções em S.O.P. | 47

- 2.7.2 Funções em P.O.S. | 52

- 2. 8. RELAÇÃO ENTRE P.O.S/S.O.P. E TABELAS-VERDADE | 55

- 2. 9. EXERCÍCIOS II | 62

- 3. MINIMIZAÇÃO DE CIRCUITOS LÓGICOS | 65

- 3. 1. MAPAS DE KARNAUGH (MK) | 66

- 3. 2. RELAÇÃO ENTRE TABELAS-VERDADE E MK'S | 72

- 3. 2.1. Para duas variáveis: / 72

- 3.2.2. Para três variáveis: | 73

- 3. 2.3. Para quatro variáveis: / 74

- 3. 3. MINIMIZAÇÃO OU SIMPLIFICAÇÃO DE FUNÇÕES ATRAVÉS DE MK'S | 75

- 3. 4. COMPLEMENTAÇÕES DE FUNÇÕES ATRAVÉS DE MK'S | 90

- 3. 5. TERMOS INDIFERENTES NA MINIMIZAÇÃO POR MK'S | 91

- 3. 6. EXERCÍCIOS III | 92

#### 4. CIRCUITOS COMBINACIONAIS | 95

- 4. 1. PROJETO DE CIRCUITO COMBINACIONAL ELEMENTAR | 96

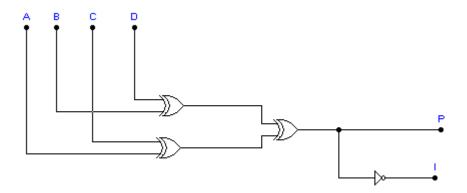

- 4. 2. CIRCUITO ELEMENTAR DE ALARME 1: | 98

- 4. 3. CIRCUITO ELEMENTAR DE ALARME 2: | 99

- 4. 4. CIRCUITO ELEMENTAR DE ALARME 3: | 101

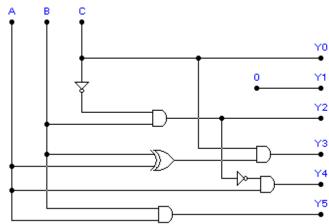

- 4. 5. CODIFICADOR ELEMENTAR X/X<sup>2</sup>: | 102

- 4. 6. COMANDO DE CIRCUITO ELÉTRICO: | 104

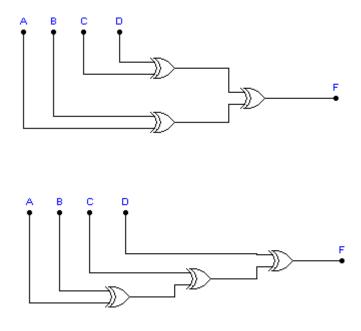

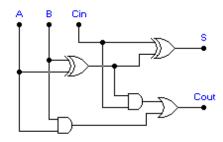

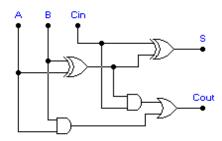

- 4. 7. SOMADOR COMPLETO OU FULL-ADDER: | 107

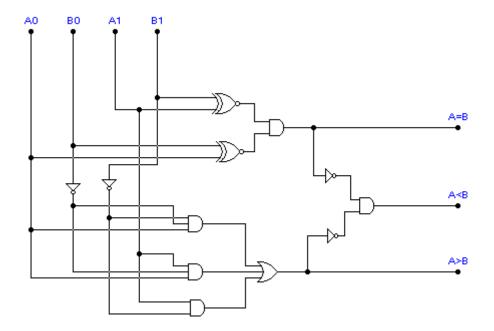

- 4. 8. CIRCUITO COMPARADOR: | 108

- 4. 9. CIRCUITO GERADOR DE BIT DE PARIDADE: | 112

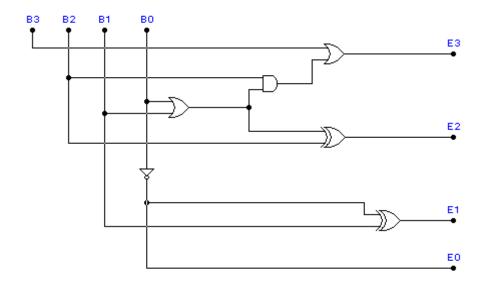

- 4. 10. CONVERSOR DE CÓDIGO BCD/ XS3: | 115

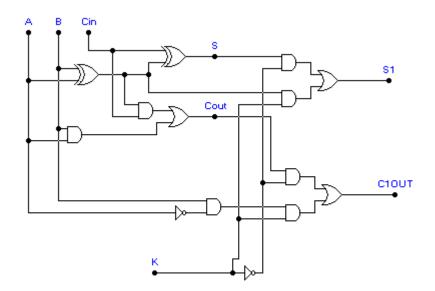

- 4. 11. SELECIONADOR SOMADOR/SUBTRATOR: | 119

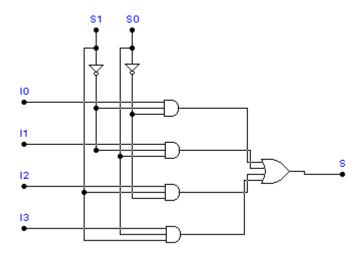

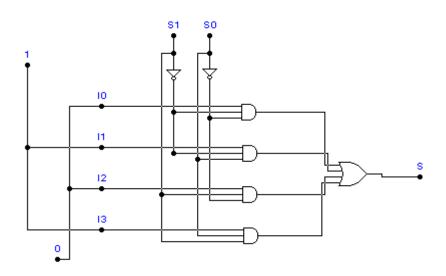

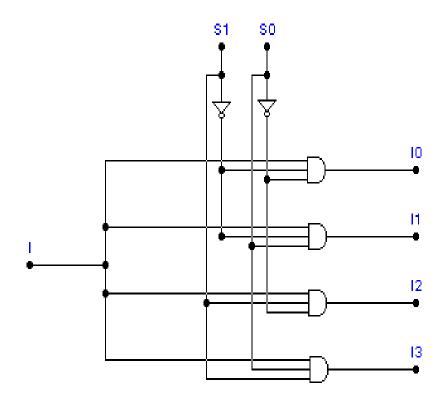

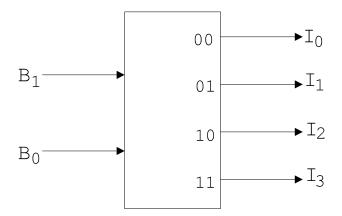

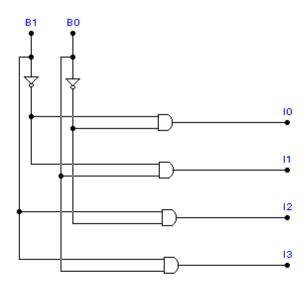

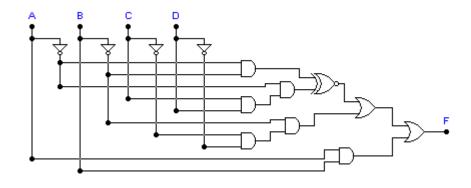

- 4. 12. MULTIPLEXADOR/DEMULTIPLEXADOR: | 122

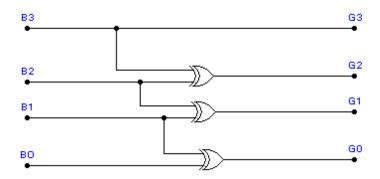

- 4. 13. CONVERSOR BINÁRIO/GRAY: | 125

- 4. 14. DECODIFICADORES: | 128

- 4. 15 CONSIDERAÇÕES GERAIS: | 130

- 4. 16. EXERCÍCIOS IV | 132

#### 5. **FLIP-FLOP's** | 135

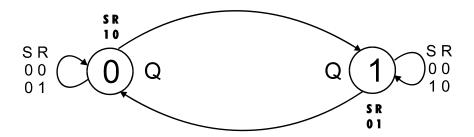

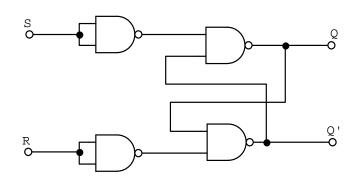

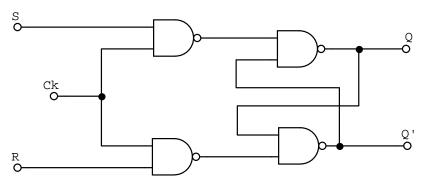

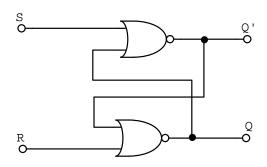

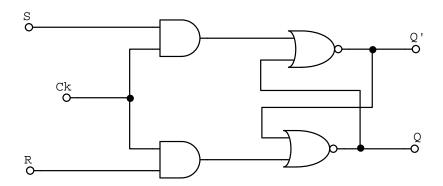

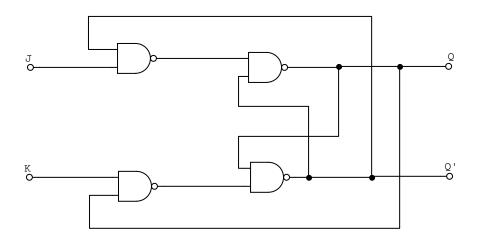

- 5.1. FLIP-FLOP SR: | 136

- 5.1.1. Diagrama de Estados FF-SR: | 136

- 5.1.2. Tabela-Característica FF-SR: | 137

- 5.1.3. Tabela de Estados FF-SR: | 137

- 5.1.4. Tabela de Excitação FF-SR: | 141

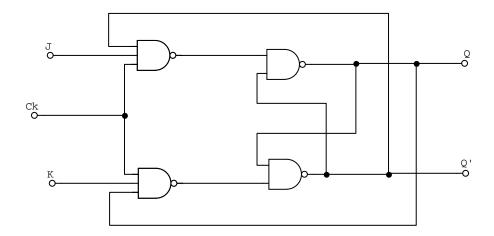

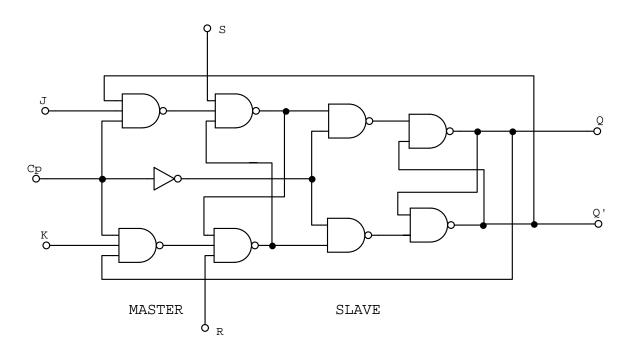

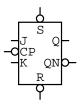

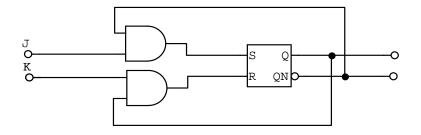

#### 5.2. FLIP-FLOP JK | 142

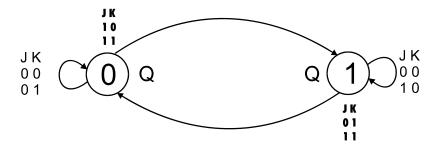

- 5.2.1. Diagrama de Estados FF-JK: | 142

- 5.2.2. Tabela-Característica FF-JK: | 143

- 5.2.3. Tabela de Estados FF-JK: | 143

- 5.2.4. Tabela de Excitação FF-JK: | 146

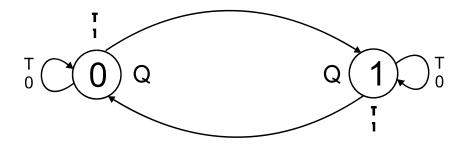

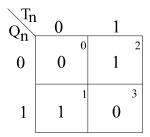

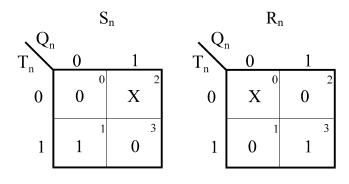

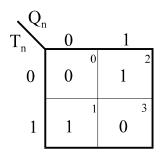

#### 5.3. FLIP-FLOP T | 147

- 5.3.1. Diagrama de Estados FF-T: | 147

- 5.3.2. Tabela Característica FF-T: | 147

- 5.3.3. Tabela de Estados FF-T: | 147

- 5.3.4. Tabela de Excitação FF-T: | 148

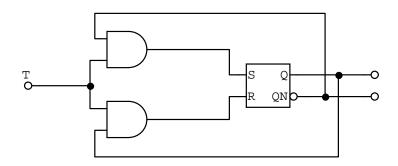

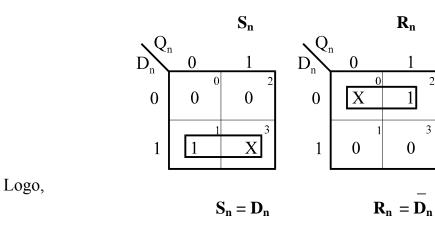

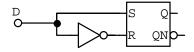

#### 5.4. FLIP-FLOP D | **149**

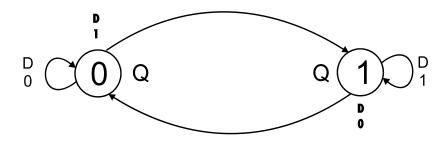

- 5.4.1. Diagrama de Estados FF-D: | 149

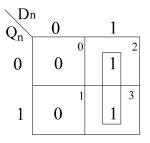

- 5.4.2. Tabela Característica FF-D: | 149

- 5.4.3. Tabela de Estados FF-D: | 150

- 5.4.4. Tabela de Excitação FF-D: | 150

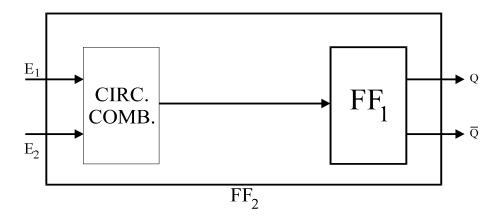

#### 5.5. CONVERSÃO DE FLIP-FLOP'S | 151

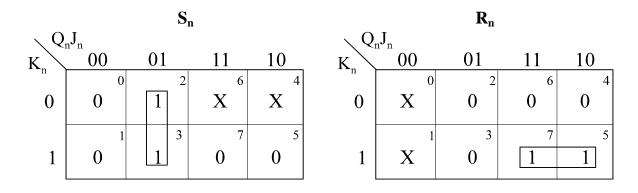

- 5.5.1. Conversão do FF SR em FF JK | 152

- 5.5.2. Conversão do FF-SR em FF-T | 153

- 5.5.3. Conversão do FF-SR em FF-D | 154

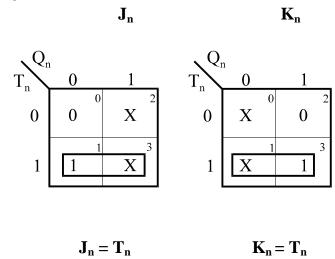

- 5.5.4. Conversão do FF-JK em FF-T | 155

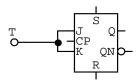

- 5.5.5.Conversão do FF-D em FF-T | 156

- 5.5.6. Conversão do FF-SR num FF qualquer | 156

# 6. IMPLEMENTAÇÃO DE CIRCUITOS LÓGICOS &

#### Field Programmable Gate Array - FPGA's | 159

- 6. 1. CONSIDERAÇÕES GERAIS | 159

- 6. 1.1. Considerações sobre a Tecnologia do FPGA / 163

- 6. 1.2. Ilustração de um FPGA | 164

- 6. 1.3. Considerações necessárias | 166

- 6. 2. PESQUISAS EM FPGA | 167

## **REFERÊNCIAS | 169**

# 1. INTRODUÇÃO AOS SISTEMAS NUMÉRICOS

Todo sistema numérico é constituído por um conjunto ordenado de símbolos ou dígitos, com regras definidas para as operações de adição, subtração, multiplicação, divisão e outras operações matemáticas. O número de símbolos pertencentes a um dado sistema é denominado **base** ou **raiz**.

Um sistema numérico permite representar uma grandeza qualquer através de símbolos pertencentes ao sistema, podendo tal representação constar de uma parte inteira e outra fracionária, as quais são separadas, entre si, por uma vírgula. Um número escrito numa base qualquer (**r**) pode ser expresso por sua forma polinomial:

$$(N)_{r} = \sum_{j=-m}^{n-1} a_{j} r^{j}$$

ou

$$(N)_r = a_{n-1} r^{n-1} + a_{n-2} r^{n-2} + ... + a_1 r^1 + a_0 r^0 +... \Rightarrow \{Parte Inteira\}$$

+  $\mathbf{a_{-1}} \ \mathbf{r^{-1}} + \mathbf{a_{-2}} \ \mathbf{r^{-2}} + \dots + \mathbf{a_{-m}} \ \mathbf{r^{-m}} \Rightarrow \{\text{Parte Fracion\'aria}\}$

onde:

$\mathbf{r} \Rightarrow \text{(base ou raiz do sistema)};$

$\mathbf{a} \Rightarrow (\text{dígito do sistema});$

n ⇒ (número de dígitos da parte inteira);

m ⇒ (número de dígitos da parte fracionária);

$\mathbf{a_{n-1}} \Rightarrow$  (dígito mais significativo da parte inteira);

$a_0 \Rightarrow$  (dígito menos significativo da parte inteira);

$a_{-1} \Rightarrow$  (dígito mais significativo da parte fracionária);

$\mathbf{a_{-m}} \Rightarrow$  (dígito menos significativo da parte fracionária).

O Sistema Decimal é o mais utilizado nas operações matemáticas e aplicações gerais da engenharia, mas alguns outros Sistemas Numéricos são de grande importância, sobretudo no estudo dos circuitos lógicos, sistemas digitais e computadores, a exemplo dos Sistemas: Binário, Octal e Hexadecimal, os quais são assim denominados em virtude de apresentarem, respectivamente, as bases dois, oito e dezesseis.

Assim, os mencionados Sistemas Numéricos possuem os dígitos abaixo discriminados:

- decimal: {0,1,2,3,4,5,6,7,8,9};

- binário: {0,1};

- octal: {0,1,2,3,4,5,6,7} e

- hexadecimal:{0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F}.

Qualquer dígito do Sistema Binário é comumente denominado *bit*, pela contração das palavras *binary digit*, do idioma inglês. O Sistema Hexadecimal (**Hex**), é considerado como um sistema alfanumérico, por ser constituído por letras do alfabeto e algarismos. As letras **A**, **B**, **C**, **D**, **E** e **F** do Hexadecimal correspondem aos decimais: **10**, **11**, **12**, **13**, **14** e **15**, respectivamente.

A representação polinomial de um número, expresso nesses sistemas de interesse, pode ser exemplificada conforme a indicação abaixo:

$$(N)_{10} = (94,72)_{10} = 9 \times 10^{1} + 4 \times 10^{0} + 7 \times 10^{-1} + 2 \times 10^{-2}$$

$$(N)_{2} = (1011,11)_{2} = 1 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0} + 1 \times 2^{-1} + 1 \times 2^{-2}$$

$$(N)_{8} = (1374,25)_{8} = 1 \times 8^{3} + 3 \times 8^{2} + 7 \times 8^{1} + 4 \times 8^{0} + 2 \times 8^{-1} + 5 \times 8^{-2}$$

$$(N)_{16} = (F8E,3D)_{16} = F \times 16^{2} + 8 \times 16^{1} + E \times 16^{0} + 3 \times 16^{-1} + D \times 16^{-2}$$

## 1.1 CONVERSÕES ENTRE SISTEMAS NUMÉRICOS

Um número expresso num dado sistema numérico tem o seu equivalente em qualquer outro sistema. Assim, um número decimal, mediante a aplicação de algoritmos adequados, poderá ter o seu equivalente binário, octal, hexadecimal ou em qualquer outra base. Do mesmo modo, um número escrito, por exemplo num sistema cuja base é igual a 3 (ternário), também terá os seus equivalentes em binário, decimal, octal, hexadecimal ou em qualquer outra base ou raiz.

A obtenção de um número equivalente a outro numa base distinta, denomina-se conversão numérica. Essencialmente, três casos devem ser considerados:

- a) conversão de um número numa base qualquer para decimal:  $(N)r \Rightarrow (N)_{10}$ ;

- b) conversão de um número decimal para uma base qualquer:  $(N)_{10} \Rightarrow (N)_r$ ;

- c) conversão de um número numa base  $r_1$  para a base  $r_2$ :  $(N)_{r_1} \Rightarrow (N)_{r_2}$ .

## 1.1.1 Conversão de um número numa Base qualquer para Decimal: $(N)_r \Rightarrow (N)_{10}$

Quando se deseja encontrar o decimal equivalente a um número expresso em qualquer outro sistema, representa-se o número em questão sob a sua forma polinomial e, em seguida, encontra-se o decimal correspondente a cada uma das parcelas. A soma resultante das diversas parcelas corresponderá ao número decimal equivalente. Por exemplo: se uma determinada grandeza se encontra representada pelo número binário  $(N)_2 = (1101,1001)_2$ , a sua expressão polinomial será:

$$(N)_2 = 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1} + 0 \times 2^{-2} + 0 \times 2^{-3} + 1 \times 2^{-4}$$

.

Encontrando-se o decimal equivalente a cada uma das parcelas, tem-se:

$$8 + 4 + 0 + 1 + 0.5 + 0 + 0 + 0.0625$$

.

Efetuando-se a soma das parcelas acima, encontra-se o número  $(13,5625)_{10}$  como resultado, o qual corresponderá ao decimal equivalente ao número binário  $(1101,1001)_2$ .

Ou seja:

$$(13,5625)_{10} \cong (1101,1001)_2$$

Do mesmo modo, se o hexadecimal  $(N)_{16} = (F8E,3D)_{16}$  tem por representação polinomial:

$$(N)_{16} = F \times (16)^2 + 8 \times (16)^1 + E \times (16)^0 + 3 \times (16)^{-1} + D \times (16)^{-2}$$

então, sabendo-se que as letras **A**, **B**, **C**, **D**, **E**, e **F** do Sistema Hexadecimal correspondem respectivamente aos números **10**, **11**, **12**, **13**, **14**, e **15** do Sistema Decimal, como dito acima, a sua representação polinomial será:

$$15 \times (16)^2 + 8 \times (16)^1 + 14 \times (16)^0 + 3 \times (16)^{-1} + 13 \times (16)^{-2}$$

ou

$3840 + 128 + 14 + 0,1875 + 0,0508$ ,

cuja soma resulta em (3982,2383)<sub>10</sub>.

Logo,

$$(3982,2383)_{10} \cong (F8E,3D)_{16}$$

Do mesmo modo, se o número  $(N)_7 = (2146,523)_7$  tem por representação polinomial:

$$2 \times 7^{3} + 1 \times 7^{2} + 4 \times 7^{1} + 6 \times 7^{0} + 5 \times 7^{-1} + 2 \times 7^{-2} + 3 \times 7^{-3}$$

e, sendo os decimais equivalentes a cada uma das parcelas:

$$686 + 49 + 28 + 6 + 0.7143 + 0.0408 + 0.0087$$

a soma dessas parcelas é igual a (769,7638)<sub>10</sub>.

Portanto,

$$(769,7638)_{10} \cong (2146,523)_{7}$$

O procedimento acima, envolvendo o desenvolvimento polinomial (**DP**) e o somatório das diversas parcelas, convertidas ao Sistema Decimal, deverá ser aplicado cada vez que um número expresso numa **base r** qualquer deva ser convertido à **base 10**.

Esquematicamente:

$$(N)_r \Rightarrow \{ \Sigma(D P) \} \Rightarrow (N)_{10}$$

.

#### Observação:

No caso específico de se converter um número binário, inteiro, em seu equivalente decimal, existe um algoritmo muito simples, conhecido como o **método de dobrar** *e* **somar**, que permite a realização de tal conversão praticamente por inspeção, sem se utilizar, explicitamente, o desenvolvimento polinomial, o qual muitas vezes se torna enfadonho, quando da sua aplicação sistemática.

O método em questão consiste em dobrar o **bit** mais significativo, e somá-lo com o imediatamente menos significativo, dobrando-se novamente o resultado, repetindo-se o processo até o **bit** menos significativo da parte inteira. O resultado, ao final, será o decimal equivalente.

#### **Exemplo:**

Encontrar o decimal equivalente ao número binário:

$$(N)_2 = 1 \ 1 \ 0 \ 1 \ 0 \ 1$$

## Solução:

```

dobra-se o MSB

1 X 2

bit seguinte:

3

3 X 2

bit seguinte:

6 +

6

dobra-se o resultado

= 6 X 2 = 12 \Rightarrow +

12 + 1 =

dobra-se o resultado

bit seguinte:

13

= 13 \quad X \quad 2 \quad = 26 \quad \Rightarrow \quad + \quad

bit seguinte:

26 + 0 =

26

dobra-se o resultado

26 \quad X \quad 2 \quad = \quad 52 \quad \Rightarrow \quad + \quad

dobra-se o resultado

52 + 1

53

LSB

```

Decimal equivalente: (53)<sub>10</sub>.

Isto é:

$$(1\ 1\ 0\ 1\ 0\ 1)_2 \cong (53)_{10}$$

#### Outro exemplo:

Encontrar o decimal equivalente ao número binário  $(N)_2 = 100111010$ . Solução:

| dobra-se o MSB:      | 1   | X | 2 | = | $2 \Rightarrow$  | + | bit seguinte: | 2   | + | 0 | = | 2   |

|----------------------|-----|---|---|---|------------------|---|---------------|-----|---|---|---|-----|

| dobra-se o resultado | 2   | X | 2 | = | 4 ⇒              | + | bit seguinte: | 4   | + | 0 | = | 4   |

| dobra-se o resultado | 4   | X | 2 | = | 8 ⇒              | + | bit seguinte: | 8   | + | 1 | = | 9   |

| dobra-se o resultado | 9   | X | 2 | = | 18 ⇒             | + | bit seguinte: | 18  | + | 1 | = | 19  |

| dobra-se o resultado | 19  | X | 2 | = | $38 \Rightarrow$ | + | bit seguinte: | 38  | + | 1 | = | 39  |

| dobra-se o resultado | 39  | X | 2 | = | 78 ⇒             | + | bit seguinte: | 78  | + | 0 | = | 78  |

| dobra-se o resultado | 78  | X | 2 | = | 156 ⇒            | + | bit seguinte: | 156 | + | 1 | = | 157 |

| dobra-se o resultado | 157 | X | 2 | = | 314 ⇒            | + | LSB:          | 314 | + | 0 | = | 314 |

Decimal equivalente:  $(314)_{10}$ .

Logo,

$$(1\ 0\ 0\ 1\ 1\ 1\ 0\ 1\ 0)_2 \cong (314)_{10}$$

Observa-se que a aplicação de algoritmo similar à parte fracionária, bem como aos números em Octal ou Hexadecimal, não reduz suficientemente o trabalho de se efetuar a conversão pelos métodos anteriormente descritos, não se justificando, portanto, a sua utilização generalizada!

# 1.1.2 Conversão de um Número Decimal para uma Base qualquer: $(N)_{10} \Rightarrow (N)_r$

Freqüentemente o número conhecido encontra-se em decimal  $(N)_{10}$  e deseja-se obter o seu equivalente numa base  $\mathbf{r}$  qualquer  $(N)_{\mathbf{r}}$ . Neste caso, o método anterior não é utilizado diretamente, sendo aplicados distintos algoritmos tanto

para a parte inteira quanto para a fracionária do decimal conhecido, procedendose do seguinte modo:

- a) separa-se a parte inteira da fracionária, caso esta última exista;

- b) toma-se a parte inteira do número decimal e divide-se pela base (r) do sistema no qual se deseja encontrar o número equivalente. O resultado apresentará um quociente (Q) e um resto (R). Toma-se o primeiro quociente encontrado e divide-se novamente pela base (r). O resultado apresentará um segundo quociente e um segundo resto. Aplica-se sucessivamente tal processo até que o quociente resultante seja nulo, indicando-se também o último resto obtido. Os restos obtidos ao longo desse procedimento se constituirão nos dígitos da parte inteira do número na base r, sendo o primeiro deles o dígito menos significativo (LSB) e o último, o mais significativo (MSB).

- c) toma-se a parte fracionária do número decimal (**F**), caso a mesma exista, e multiplica-se pela base (**r**) do sistema no qual se deseja encontrar o número equivalente. O resultado apresentará um produto (**P**) que estará constituído por uma parte inteira (**I**), eventualmente nula, e outra fracionária (**f**). Toma-se a primeira parte fracionária encontrada e multiplica-se novamente pela base (**r**). O resultado apresentará um segundo produto, também constituído por uma segunda parte inteira, eventualmente nula, e outra fracionária.

Repete-se o procedimento, sucessivamente, até o número de dígitos atender à aproximação necessária para representar com precisão o equivalente ao decimal a ser convertido, ou até a parte fracionária resultar nula, ou se configurar como em sendo uma dízima periódica!

Os inteiros obtidos ao longo desse procedimento se constituirão nos dígitos da parte fracionária do número na base (r), sendo o primeiro deles o dígito mais significativo (MSB) e o último, o menos significativo (LSB)!

Após tal procedimento, a soma do inteiro com o fracionário equivalentes, resulta no número representado na base (**r**).

Exemplo: Converter o decimal  $(N)_{10} = 100,39$  para o sistema binário.

## Solução:

a) Separando-se a parte inteira da fracionária, temos que o número decimal acima (N) $_{10}$  = 100,39 pode ser escrito como:

$$(N)_{10} = (100)_{10} + (0,39)_{10}$$

b) Tomando-se a parte inteira  $(100)_{10}$  e aplicando-se o procedimento b, indicado anteriormente, tem-se:

| DEC | ÷ | Base | = | Quociente | + | Resto |               | Status  |

|-----|---|------|---|-----------|---|-------|---------------|---------|

| 100 | ÷ | 2    | = | 50        | + | 0     | $\Rightarrow$ | [LSB]   |

| 50  | ÷ | 2    | = | 25        | + | 0     |               |         |

| 25  | ÷ | 2    | = | 12        | + | 1     |               |         |

| 12  | ÷ | 2    | = | 6         | + | 0     |               |         |

| 6   | ÷ | 2    | = | 3         | + | 0     |               |         |

| 3   | ÷ | 2    | = | 1         | + | 1     |               |         |

| 1   | ÷ | 2    | = | 0         | + | 1     | $\Rightarrow$ | [ MSB ] |

Assim, o número binário equivalente ao inteiro  $(100)_{10}$  será constituído pelos dígitos binários: 1 1 0 0 1 0 0.

Ou seja:

$$(1100100)_2 \cong (100)_{10}$$

c) Tomando-se agora a parte fracionária  $(0,39)_{10}$  e aplicando-se o procedimento c, indicado acima, tem-se:

| DEC  | X | Base | = | Produto | = | Fração | + | Inteira |               | Status  |

|------|---|------|---|---------|---|--------|---|---------|---------------|---------|

| 0,39 | X | 2    | = | 0,78    | = | 0,78   | + | 0       | $\Rightarrow$ | [ MSB ] |

| 0,78 | X | 2    | = | 1,56    | = | 0,56   | + | 0       |               |         |

| 0,56 | X | 2    | = | 1,12    | = | 0,12   | + | 1       |               |         |

| 0,12 | X | 2    | = | 0,24    | = | 0,24   | + | 1       |               |         |

| 0,24 | X | 2    | = | 0,48    | = | 0,48   | + | 0       |               |         |

| 0,48 | X | 2    | = | 1,92    | = | 0,96   | + | 0       |               |         |

| 0,96 | X | 2    | = | 1,92    | = | 0,92   | + | 0       |               |         |

| 0,92 | X | 2    | = | 1,84    | = | 0,84   | + | 1       |               |         |

| 0,84 | X | 2    | = | 1,68    | = | 0,68   | + | 1       |               |         |

| 0,68 | X | 2    | = | 1,36    | = | 0,36   | + | 1       | $\Rightarrow$ | [LSB]   |

Assim, a parte fracionária será constituída pelos dígitos binários:

#### 0110001111

Observa-se que a fração resultante igual a  $(0,0110001111)_2$ , corresponde na verdade ao decimal  $(0,3896)_{10}$  - o que pode ser verificado através do seu desenvolvimento polinomial; ou seja, uma aproximação do número  $(0,39)_{10}$ . O erro na conversão é inversamente proporcional ao número de *bits* da parte fracionária.

Concluída a conversão da parte fracionária, tem-se então que:

$$(100,39)_{10} \cong (1100100,0110001111)_2$$

Evidentemente, a verificação desse resultado pode ser realizada pela conversão do binário encontrado ao decimal correspondente, através do método do desenvolvimento polinomial, conforme citado acima, considerando as aproximações pertinentes.

Vale ressaltar que o resultado da conversão será exato somente quando a parte fracionária resultar nula.

#### Por exemplo: Converter o decimal 0,5 para a base 2.

Aplicando-se o mesmo procedimento, anteriormente descrito, para a parte fracionária, uma vez que neste caso a parte inteira é nula, tem-se:

**DEC** x Base = Produto = Fração + Inteira Status

$$0.5$$

x  $2$  =  $1.0$  =  $0.0$  +  $1 \Rightarrow [MSB]$

$0.0$  x  $2$  =  $0.0$  =  $0.0$  +  $0 \Rightarrow [LSB]$

O binário equivalente é constituído pelos bits **1** e **0**. Isto é:

$$(0,5)_{10} \cong (0,10)_{2}$$

A conversão de um número na base dez, no seu equivalente em qualquer outra base pode ser encontrada utilizando-se o método acima exposto. Este algoritmo se aplica a qualquer caso, lembrando-se apenas que, quando o número é composto, as partes inteira e fracionária recebem tratamentos distintos e duais.

#### Esquematicamente, para efeito mnemônico,

$$\left\{\begin{array}{l} \mathbf{I} \div \mathbf{r} = \mathbf{Q} + [\mathbf{R}]^{\mathrm{LSB}}_{\mathrm{MSB}} \right\} \\ \\ (\mathbf{N})_{\mathbf{10}} \Rightarrow \quad \left\{\begin{array}{c} + \\ \mathbf{F} \times \mathbf{r} = \mathbf{f} + [\mathbf{I}]^{\mathrm{MSB}}_{\mathrm{LSB}} \end{array}\right\} \Rightarrow (\mathbf{N})_{\mathbf{r}}$$

#### 1.1.3 Conversão de um Número numa Base $r_1$ para a Base $r_2$ : $(N)r_1 \Rightarrow (N)r_2$

Genericamente, quando se deseja converter um número expresso num sistema cuja base ou raiz é definida por  $\mathbf{r_1}$  em outro sistema cuja base é definida por  $\mathbf{r_2}$ , procede-se da seguinte maneira:

Encontra-se o equivalente decimal do número expresso em um dos sistemas através do seu desenvolvimento polinomial, como indicado no item I.1.1. Após a identificação do decimal correspondente, encontra-se o equivalente ao número expresso na outra base, através do método indicado no item I.1.2.

Esquematicamente:

$$(N)r_1 \Rightarrow \Rightarrow (N)_{10} \Rightarrow \Rightarrow (N)r_2$$

Exemplo: Encontrar o equivalente ao número (123,45)<sub>6</sub>, num sistema de base 3.

Solução: O equivalente decimal de (123,45)<sub>6</sub> é, como já vimos pelo método do desenvolvimento polinomial, encontrado por:

$$1 \times 6^{2} + 2 \times 6^{1} + 3 \times 6^{0} + 4 \times 6^{-1} + 5 \times 6^{-2} \quad \text{ou},$$

$$1 \times 36 + 2 \times 6 + 3 \times 1 + 4 \times 0,1666 + 5 \times 0,0277 \quad \text{ou ainda},$$

$$36 + 12 + 3 + 0,6664 + 0,1385 = (51,8049)_{10}.$$

Então:

$$(123,45)_{6} \cong (51,8049)_{10}$$

Para se encontrar o equivalente de  $(51,8049)_{10}$  na base 3, aplica-se o algoritmo indicado no item I.1.2, separando-se o procedimento relativo à parte inteira do da fracionária, conforme visto anteriormente:

#### Parte inteira:

DEC

$$\div$$

Base

=

Quociente

+

Resto

Status

51

$\div$

3

=

17

+

0

$\Rightarrow$

[LSB]

17

$\div$

3

=

5

+

2

5

$\div$

3

=

1

+

2

1

$\div$

3

=

0

+

1

$\Rightarrow$

[MSB]

ou,

$$(51)_{10} \cong (1220)_3$$

## Parte Fracionária:

| DEC.   | X | Base | = | Produto | = | Fração | + | Inteira |               | <b>Status</b> |

|--------|---|------|---|---------|---|--------|---|---------|---------------|---------------|

| 0,8049 | X | 3    | = | 2,4147  | = | 0,4147 | + | 2       | $\Rightarrow$ | [ MSB ]       |

| 0,4147 | X | 3    | = | 1,2441  | = | 0,2441 | + | 1       |               |               |

| 0,2441 | X | 3    | = | 0,7323  | = | 0,7323 | + | 0       |               |               |

| 0,7323 | X | 3    | = | 2,1969  | = | 0,1969 | + | 2       |               |               |

| 0,1969 | X | 3    | = | 0,5907  | = | 0,5907 | + | 0       |               |               |

| 0,5907 | X | 3    | = | 1,7721  | = | 0,7721 | + | 1       |               |               |

| 0,7721 | X | 3    | = | 2,3163  | = | 0,3163 | + | 2       | $\Rightarrow$ | [LSB]         |

ou,

$$(0,8049)_{10} \cong (0,2102012...)_{3}$$

Logo,

$$(123,45)_6 \cong (51,8049)_{10} \cong (1220,2102012...)_3$$

## 1.1.4 Conversões entre Binário, Octal e Hexadecimal

A conversão entre os sistemas binário, octal e hexadecimal, pode ser realizada a partir do método geral indicado no item I.1.3. Contudo, devido a determinadas peculiaridades desses sistemas, a conversão entre os mesmos torna-se muito simples, desde que se considere o seguinte: Os dígitos do sistema octal podem ser representados por grupos de 3 *bits* do sistema binário, como a seguir:

| OCTAL | BINÁRIO |

|-------|---------|

| 0     | 000     |

| 1     | 001     |

| 2     | 010     |

| 3     | 011     |

| 4     | 100     |

| 5     | 101     |

| 6     | 110     |

| 7     | 111     |

Do mesmo modo, os dígitos do sistema hexadecimal podem ser representados por grupos de 4 bits do sistema binário:

| HEXADECIMAL | BINÁRIO |

|-------------|---------|

| 0           | 0000    |

| 1           | 0001    |

| 2           | 0010    |

| 3           | 0011    |

| 4           | 0100    |

| 5           | 0101    |

| 6           | 0110    |

| 7           | 0111    |

| 8           | 1000    |

| 9           | 1001    |

| A           | 1010    |

| В           | 1011    |

| С           | 1100    |

| D           | 1101    |

| Е           | 1110    |

| F           | 1111    |

Pela razão acima citada, qualquer número binário pode ser convertido diretamente em octal ou hexadecimal, bastando para isso separar-se no primeiro caso (**octal**) grupos de 3 *bits* e, no segundo (**hexadecimal**), grupos de 4 *bits* do binário em questão. A partir daí, identifica-se a representação equivalente, encontrando-se, por inspeção, o resultado num ou noutro sistema.

Quando o grupo de dígitos não pode ser subdividido em subgrupos de 3 ou 4 *bits*, acrescentam-se zeros à esquerda da parte inteira ou à direita da parte fracionária.

#### Exemplo: Encontrar o octal e o hexadecimal equivalentes ao número

$$(N)_2 = 111101000,0111$$

Solução: Separando-se a informação em grupos de 3 bits,

$$(N)_2 = 111 \quad 101 \quad 000, \quad 011 \quad 100 \quad ou,$$

$(N)_8 = 7 \quad 5 \quad 0 \quad , \quad 3 \quad 4$

Do mesmo modo, no caso do hexadecimal, separando-se em grupos de 4 bits,

$$(N)_2 = 0001$$

1110 1000, 0111 tem-se:

$(N)_{16} = 1$  E 8, 7.

Logo,

$$(111101000,0111)_2 \cong (750,34)_8 \cong (1E8,7)_{16}$$

Observa-se então que, o número de dígitos necessários para se representar uma determinada grandeza varia de acordo com a base do sistema. No exemplo acima, a grandeza é representada em binário por 13 dígitos, em octal por 5 dígitos e por apenas 4 dígitos em hexadecimal. Essa é uma das vantagens de se utilizar os sistemas octal e hexadecimal!

Evidentemente, o processo de conversão de octal ou hexadecimal para binário também é possível, bastando aplicar o processo anterior de modo inverso.

# **Exemplo:**

Encontrar o Bnário equivalente ao Octal  $(N)_8 = 274,71$

Como

$$(N)_8 = 2 7 4 , 7 1$$

tem-se

$$(N)_2 = 010 \ 111 \ 100 \ , \ 111 \ 001.$$

Do mesmo modo, o hexadecimal  $(N)_{16}$  = FAE,BC terá como equivalente o binário:

$$(N)_{16} = F A E , B C ou$$

$$(N)_2 = 1111 \quad 1010 \quad 1110, \quad 1011 \quad 1100$$

#### Observações:

Quando se deseja encontrar os equivalentes numéricos em binário, octal e hexadecimal de um determinado número explicitado em decimal, deve-se iniciar o processo de conversão a partir do hexadecimal, e não do binário como é muito comum se proceder. A razão dessa recomendação nasce do fato de as operações de conversão para a base 16 convergir mais rapidamente para o resultado. Após a determinação do hexadecimal, deve-se encontrar, por inspeção, o seu equivalente binário e, através desse mesmo processo, a partir do binário, encontrar-se o octal equivalente.

Devido à sua grande utilização, vale dizer que os binários, quando agrupados em determinado número de dígitos, constituíndo-se numa informação completa, recebe designações especiais a saber:

- BIT ⇒ um dígito binário 0 ou 1

- $NIBBLE \Rightarrow um grupo de 4 bits$

- BYTE  $\Rightarrow$  um grupo de 8 bits

- WORD  $\Rightarrow$  um grupo de 2 bytes ou 4 nibbles, ou múltiplos desses.

Apenas como ilustração, apresenta-se a seguir algumas equivalências numéricas entre os sistemas decimal, binário, octal e hexadecimal:

| DECIMAL | BINÁRIO    | OCTAL | HEXADECIMAL |

|---------|------------|-------|-------------|

| 0       | 00000      | 0     | 0           |

| 1       | 00001      | 1     | 1           |

| 2       | 00010      | 2     | 2           |

| 3       | 00011      | 3     | 3           |

| 4       | 00100      | 4     | 4           |

| 5       | 00101      | 5     | 5           |

| 6       | 00110      | 6     | 6           |

| 7       | 00111      | 7     | 7           |

| 8       | 01000      | 10    | 8           |

| 9       | 01001      | 11    | 9           |

| 10      | 01010      | 12    | A           |

| 11      | 01011      | 13    | В           |

| 12      | 01100      | 14    | С           |

| 13      | 01101      | 15    | D           |

| 14      | 01110      | 16    | E           |

| 15      | 01111      | 17    | F           |

| 16      | 10000      | 20    | 10          |

| 17      | 10001      | 21    | 11          |

| 18      | 10010      | 22    | 12          |

| 19      | 10011      | 23    | 13          |

| 20      | 10100      | 24    | 14          |

| 21      | 10101      | 25    | 15          |

| 22      | 10110      | 26    | 16          |

| 23      | 10111      | 27    | 17          |

| 24      | 11000      | 30    | 18          |

| 25      | 11001      | 31    | 19          |

| 26      | 11010      | 32    | 1A          |

| 27      | 11011      | 33    | 1B          |

| 28      | 11100      | 34    | 1C          |

| 29      | 11101      | 35    | 1D          |

| 30      | 11110      | 36    | 1E          |

| 31      | 11111      | 37    | 1F          |

| 32      | 100000     | 40    | 20          |

| 50      | 110010     | 62    | 32          |

| 60      | 111100     | 74    | 3C          |

| 64      | 1000000    | 100   | 40          |

| 100     | 1100100    | 144   | 64          |

| 255     | 11111111   | 377   | FF          |

| 1000    | 1111101000 | 1750  | 3E8         |

| 1024    | 1000000000 | 2000  | 400         |

#### 1.2 CÓDIGOS BINÁRIOS

A representação dos números binários nem sempre é estabelecida a partir da sua equivalência direta com os números decimais, octais ou hexadecimais, conforme indicado anteriormente. Freqüentemente, por razão de praticidade, aumento de velocidade das operações lógicas e simplificação dos circuitos digitais (hardware) que executam operações lógicas diversas, sobretudo no que diz respeito a circuitos aritméticos de computadores, torna-se conveniente expressar determinadas informações de uma forma codificada, sem que a mesma guarde qualquer relação com o valor numérico, propriamente dito, que se encontra simbolizado por um determinado número em binário. Assim, existem vários códigos numéricos dentro do próprio sistema binário. Entre esses códigos destacam-se:

- Código binário natural (8 4 2 1 )

- BCD (Binary Coded Decimal)

- Código de Gray

- Código Excesso de 3 (XS3)

- Código ASCII

- Códigos de paridade, deteção e correção de erros, etc.

A aplicação de cada um desses códigos depende de aspectos operacionais e da filosofia utilizada em projetos de circuitos aritméticos, por exemplo. As justificativas para a utilização de cada um deles, evidentemente, fogem ao escopo de uma abordagem introdutória sobre sistemas numéricos. Contudo, o código **BCD** (8421) e o **Código de Gray**, devido a aplicações que serão vistas a seguir, merecem algum destaque:

O código **BCD** (8421) representa os decimais de 0 a 9 sob a forma de 4 bits, de modo que a conversão de decimal para binário é realizada dígito a dígito.

#### **Exemplo:**

Encontrar o equivalente BCD do número decimal (1990,47)<sub>10</sub>.

$$(N)_{10} = (1990,47)_{10} = 1 \qquad 9 \qquad 9 \qquad 0 \quad , \quad 4 \qquad 7$$

Daí,

$$(N)_{BCD} = 0001 \ 1001 \ 1001 \ 0000, \ 0100 \ 0111$$

Observa-se que os decimais acima do dígito 9, não têm correspondência direta no código BCD, sendo representados dígito a dígito nesse código. Assim, por exemplo, os decimais 10 e 15 terão os seus equivalentes BCD, conforme indicado abaixo:

$$(10)_{10} \cong (0001\ 0000)_{BCD} \ e \ (15)_{10} \cong (0001\ 0101)_{BCD}$$

Os estados lógicos que não têm correspondência direta nos códigos binários, são denominados **estados indiferentes** e, como será visto na abordagem sobre Minimização de Circuitos Combinacionais e Seqüenciais, tais estados são de grande utilidade na simplificação de circuitos lógicos. O Código de Gray, por seu turno, tem a peculiaridade, como pode ser observado no quadro correspondente, de representar os equivalentes decimais na ordem crescente ou decrescente de modo que, de uma representação à outra, somente um único **bit** assume valor diferente com relação à configuração anterior. Essa característica é de grande importância em transmissão de dados e também em codificadores e conversores digitais, como será mostrado oportunamente.

A tabela apresentada abaixo mostra alguns códigos utilizados, com o objetivo de ilustrar a total inexistência da relação entre determinados códigos e o valor numérico decimal da configuração binária propriamente dito. A razão técnica de diversas codificações poderá ser encontrada na literatura especializada, e em vários trabalhos indicados na bibliografia citada.

| DEC | BIN  | BCD  | XS3  | GRAY | BIQUINARY |

|-----|------|------|------|------|-----------|

| 0   | 0000 | 0000 | 0011 | 0000 | 0100001   |

| 1   | 0001 | 0001 | 0100 | 0001 | 0100010   |

| 2   | 0010 | 0010 | 0101 | 0011 | 0100100   |

| 3   | 0011 | 0011 | 0110 | 0010 | 0101000   |

| 4   | 0100 | 0100 | 0111 | 0110 | 0110000   |

| 5   | 0101 | 0101 | 1000 | 0111 | 1000001   |

| 6   | 0110 | 0110 | 1001 | 0101 | 1000010   |

| 7   | 0111 | 0111 | 1010 | 0100 | 1000100   |

| 8   | 1000 | 1000 | 1011 | 1100 | 1001000   |

| 9   | 1001 | 1001 | 1100 | 1101 | 1010000   |

| 10  | 1010 |      |      | 1111 |           |

| 11  | 1011 |      |      | 1110 |           |

| 12  | 1100 |      |      | 1010 |           |

| 13  | 1101 |      |      | 1011 |           |

| 14  | 1110 |      | _    | 1001 |           |

| 15  | 1111 |      |      | 1000 |           |

A seguir apresenta-se uma série de exercícios propostos, objetivando-se uma revisão geral sobre o assunto aqui discutido, enfatizando-se os aspectos conceituais relativos aos diversos sistemas numéricos.

# 1.3 EXERCÍCIOS I:

#### I.1 Escrever os números abaixo sob a forma de representação polinominal:

```

a) (1001)<sub>2</sub>; b) (0,101)<sub>2</sub>; c) (101,02)<sub>3</sub>; d) (1010,01)<sub>2</sub>; e) (715)<sub>8</sub>;

f) (157,75)<sub>8</sub>; g) (1400,320)<sub>7</sub>; h) (100)<sub>8</sub>; i) (78E5,A)<sub>16</sub>; j) (0,A27)<sub>16</sub>

```

# I.2 Converter os números abaixo para o sistema numérico decimal:

```

a) (101)<sub>2</sub>; b) (1101,101)<sub>2</sub>; c) (1110,01)<sub>2</sub>; d) (0,0101)<sub>2</sub>; e) (07,602)<sub>8</sub>; f) (27,36)<sub>8</sub>; g) (0,004)<sub>8</sub>; h) (7,77)<sub>8</sub>; i) (76FA,6B)<sub>16</sub>; j) (6BA,3A)<sub>16</sub>

```

# I.3 Converter os seguintes números decimais em binários:

```

a) 0,50; b) 0,25; c) 14,776; d) 9,25; e) 10,4; f) 512,64; g) 734; h) 1010,01; i) 7836; j) 832,17.

```

#### I.4 Quantos algarismos binários necessitamos para representar os decimais:

```

a) 256; b) 512; c) 2748; d) 10844; e) 1023; f) 1024

```

#### I.5 Converter os seguintes decimais para as bases octal e hexadecimal.

```

a) 10,84; b) 36; c) 74; d) 700; e) 2700; f) 8742,34; g) 10000 h) 278,50; i) 0,0522; j) 888 k) 386; l) 222

```

# I.6 Converter diretamente da base binária para a base octal e hexadecimal os seguintes números:

```

a) 1011101; b) 110001; c) 111000; d) 111110; e) 1101101; f) 1001,1110; g) 1101001; h) 11,001; i) 0,1101; j) 110011,10110

```

# I.7 Em que base r o número 106 equivale a 577 ?

#### I.8 Em que base r o número decimal 79 equivale ao número 142?

# I.9 Em que base $\, r \,$ o decimal 22213 equivale a 106 ?

# I.10 Converter os números abaixo, conforme indicado:

- a) (543,21)<sub>6</sub> para a base 9;

- b) (42,21)<sub>5</sub> para a base 3;

- c) (52)<sub>7</sub> para a base 6

- d)  $(0,00125)_{10}$  para as bases 2, 8 e 16;

- e)  $(FEA6,FE2)_{16}$  para a base 7

# 2. INTRODUÇÃO À ÁLGEBRA BOOLEANA

Os operadores, postulados e teoremas da álgebra tradicional (não booleana), que são aplicados de uma maneira sistemática na engenharia, têm o sistema numérico decimal como referência, utilizando as suas regras básicas para adição, subtração, multiplicação, divisão e outras operações matemáticas.

A álgebra booleana, que estuda as leis e processos formais de operações aplicados ao sistema binário, é assim denominada em homenagem ao matemático inglês George Boole, o qual em 1849 publicou o livro *An Investigation of the Laws of Thought, on Which are Founded the Mathematical Theories of Logic and Probability*, apresentando os princípios básicos dessa álgebra, através de uma investigação eminentemente teórica.

Conforme citação de diversos autores, somente em 1938 Shannon, C.F. veio a publicar *Symbolic Analysis of Relay and Switching Circuits* (Trans. AIEE, 57 (1938) p 713-723), implementando aplicações práticas para o trabalho teórico de George Boole. As aplicações discernidas por Shannon transformaram radicalmente a abordagem lógica das interconexões de circuitos operados por relés, sendo tais aplicações rapidamente extendida aos componentes eletrônicos tais como válvulas termoiônicas, logo em seguida aos circuitos a transistores e, modernamente, aos circuitos integrados.

A Álgebra Booleana, por se fundamentar no Sistema Binário, o qual possui apenas os dígitos **0** e **1**, é aplicável genericamente a qualquer situação lógica envolvendo variáveis que podem assumir somente dois valores discretos, mutuamente exclusivos entre sí, tais como: [baixo, alto]; [verde, azul]; [direita, esquerda]; [0,1]; [aberto, fechado]; [-5, +12]; [falso, verdadeiro]; [morto, vivo], etc.

Assim, qualquer operação lógica realizada através da álgebra booleana que associe, ou codifique, uma ou mais variáveis como em sendo **0** ou **1**, não significa, necessariamente, que a variável ou variáveis em questão apresentem o valor numérico 0 ou 1. Tais associações, ou codificações, têm uma conotação de carater eminentemente lógico, para permitir a aplicação da álgebra booleana.

Cada vez que uma dada variável ou uma dada situação é **falsa** ou **verdadeira**, por exemplo, pode-se associar a primeira condição a **0** e a segunda a **1**.

O estabelecimento dessa convenção ou codificação é chamada de lógica positiva, por associar o **0** a uma situação "desfavorável", e o **1** a uma situação "favorável". A convenção oposta é, portanto, definida como lógica negativa. O fato de se convencionar de uma forma ou doutra, evidentemente, não altera a sistemática algébrica definida por Boole. Deve-se lembrar que, o que é definido como "desfavorável" para um observador, pode ser altamente "favorável" para outro...

#### 2.1 OPERADORES DA ÁLGEBRA BOOLEANA

Os operadores fundamentais da Álgebra Booleana são basicamente:: NOT, AND e o OR.

A aplicação do operador **NOT** a uma variável "X" é simbolizada por  $\overline{X}$  ou X'. Tal operador tem a propriedade de negar o estado lógico atribuído à variável, como ilustra a tabela abaixo:

| X | X' |

|---|----|

| 0 | 1  |

| 1 | 0  |

Esta tabela é denominada tabela-verdade.

A tabela-verdade do operador **AND** aplicado às variáveis "**X**" e "**Y**", cuja operação é simbolizada por (**X** · **Y**), ou apenas **XY**, é definida por:

| XY  | X.Y |

|-----|-----|

| 0 0 | 0   |

| 0 1 | 0   |

| 1 0 | 0   |

| 1 1 | 1   |

Ou seja, o operador "AND" faz com que o resultado da sua aplicação se torne verdadeiro (estado lógico 1), somente quando todas as variáveis envolvidas assumem valores lógicos verdadeiros.

A tabela-verdade do operador " $\mathbf{OR}$ " aplicado às variáveis " $\mathbf{X}$ " e " $\mathbf{Y}$ ", cuja operação é simbolizada por ( $\mathbf{X} + \mathbf{Y}$ ), é definida por:

| ΧY  | X + Y |

|-----|-------|

| 0 0 | 0     |

| 0 1 | 1     |

| 1 0 | 1     |

| 1 1 | 1     |

ou seja, o operador "**OR**" faz com que o resultado da sua aplicação se torne verdadeiro quando qualquer uma das variáveis assume valor lógico verdadeiro.

Vale ressaltar que as representações  $(X \cdot Y)$  para a aplicação do operador AND e também (X + Y) para o operador OR, não têm o mesmo significado das operações de multiplicação e adição, respectivamente, como acontece no sistema decimal.

Os três operadores acima mencionados são os operadores básicos da álgebra de Boole. Entretanto, devido à grande freqüência com que aparecem nas operações booleanas, outros operadores ou funções derivados deles, a partir da combinação dos operadores **NOT** com os operadores **AND** e **OR**, merecem destaque, a exemplo dos operadores **NAND**, **NOR**, **XOR** e **XNOR**, cujas tabelas-verdade são definidas abaixo:

| XY  | NAND | NOR | XOR | XNOR |

|-----|------|-----|-----|------|

| 0 0 | 1    | 1   | 0   | 1    |

| 0 1 | 1    | 0   | 1   | 0    |

| 1 0 | 1    | 0   | 1   | 0    |

| 1 1 | 0    | 0   | 0   | 1    |

Cada um desses operadores são representados da maneira indicada a seguir, e são o resultado da aplicação dos operadores fundamentais, conforme mostrado:

$$NAND(X,Y) = \overline{XY}$$

ou  $(XY)'$ :

Ao contrário do operador **AND**, a função "**NAND**" faz com que o resultado da sua aplicação se torne **falso** (estado lógico **0**) somente quando as variáveis envolvidas assumem valores lógicos **verdadeiros**.

$$NOR(X,Y) = X+Y \text{ ou } (X+Y)'$$

:

De modo análogo, a função "**NOR**" faz com que o resultado da sua aplicação se torne **falso** quando qualquer uma das variáveis assume valor lógico **verdadeiro**.

$$XOR(X,Y) = (X \oplus Y) = XY + XY$$

ou  $X'Y + XY'$ :

A função **XOR** (ou **OR**-exclusivo) é verdadeira quando uma das variáveis é **falsa** e a outra verdadeira, ou seja, quando as variáveis envolvidas assumem valores lógicos **diferentes**, simultaneamente.

$$XNOR(X,Y) = X \odot Y = XY + XY \text{ ou } X'Y' + XY$$

:

Ao contrário da função **XOR**, a **XNOR** (ou **NOR-exclusivo**) é verdadeira somente quando as variáveis envolvidas assumem o mesmo valor lógico, simultaneamente. Esta função, por este motivo, é também conhecida como *função coincidência*.

Observar que a função **XNOR** é o resultado da aplicação do operador **NOT** à função XOR; isto é:

$$X \odot Y = X \oplus Y$$

#### 2.2 CIRCUITOS EQUIVALENTES E SIMBOLOGIA C.I.'s

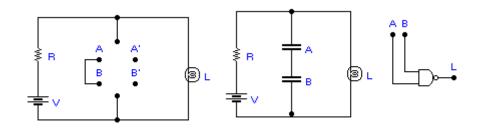

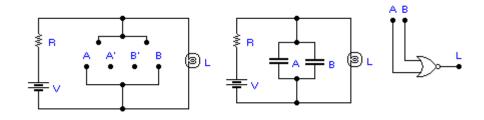

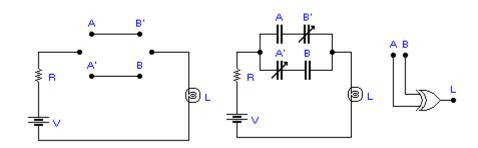

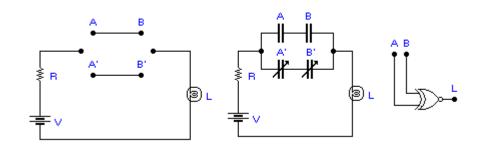

Antes do estudo dos postulados e teoremas da Álgebra de Boole, torna-se extremamente interessante identificar-se os circuitos equivalentes inerentes a cada uma das funções anteriormente apresentadas. O conhecimento de tais circuitos equivalentes auxilia sobremaneira o entendimento das relações algébricas, permitindo uma visão conceitual dos teoremas, postulados e propriedades da álgebra em questão.

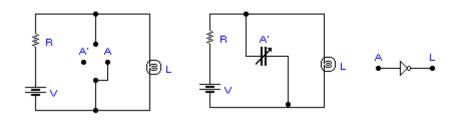

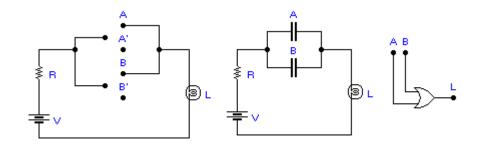

Para o desenvolvimento dos circuitos equivalentes, utilizam-se chaves convencionais ou contatos de relés (**X** e **X**'), uma fonte de tensão (**V**), um resistor (**R**) e uma carga, simbolizada por uma lâmpada (**L**). O estado lógico **1** estará associado a: contato fechado ou bobina do relé energizada ou lâmpada acesa. O estado lógico **0** estará associado às situações: contato aberto ou bobina do relé desenergizada ou lâmpada apagada!

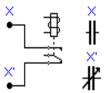

O relé representado abaixo, como se vê, possui dois contatos. Um deles encontrase permanentemente fechado (estado lógico 1) na condição de repouso, ou seja, quando a bobina não se encontra energizada (estado lógico 0); este contato está sendo definido como X'. O outro contato (X) atua de modo oposto: encontra-se aberto (estado lógico 0) na condição de repouso. Quando a bobina do relé passa a estar energizada (estado lógico 1), os dois contatos mudam de estado: X' que se encontrava em estado lógico 1 (contato fechado), muda para o estado lógico 0 (contato aberto), enquanto X que se encontrava no estado lógico 0, muda para o estado 1. O funcionamento desses contatos encontra-se representado pelos símbolos indicados ao lado dos mesmos, no diagrama abaixo

Os operadores básicos e os seus derivados mais utilizados, acima definidos sob a forma de *tabelas-verdade*, são simulados a seguir por circuitos elétricos muito simples, tendo ao lado o diagrama correspondente em contatos de relés e ainda a simbologia própria dos circuitos lógicos integrados (**C.I.**'s), para cada uma das portas lógicas, conforme aparecem nos diagramas eletrônicos dos circuitos lógicos ou digitais.

NOT:  $L = \overline{A}$  ou L = A'

AND: L = A . B

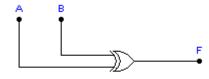

# **OR:** L = A + B

NAND:  $L = \overline{A \cdot B}$  ou  $L = (A \cdot B)$

**NOR:** L = A + B ou L = (A + B)

$XOR: L = A \oplus B = A \cdot B + A \cdot B$  ou  $L = (A' \cdot B + A \cdot B')$

# **XNOR:** $L = A \odot B = A \cdot B + A \cdot B$ ou $L = (A' \cdot B' + A \cdot B)$

# 2.3 POSTULADOS E TEOREMAS DA ÁLGEBRA BOOLEANA

Após a associação de cada um dos operadores ou funções com os seus circuitos equivalentes, torna-se muito simples a interpretação dos postulados, teoremas e propriedades apresentados abaixo:

#### **Postulados:**

| NOT   | AND     | OR        |

|-------|---------|-----------|

|       | 0.0 = 0 | 0+0=0     |

|       | 0.1 = 0 | 0 + 1 = 1 |

| 1 = 0 | 1.0 = 0 | 1 + 0 = 1 |

|       | 1.1=1   | 1 + 1 = 1 |

# **Teoremas e Propriedades:**

#### 1. Sobre "1" e "0"

$$0 + X = X$$

$0 \cdot X = 0$   $1 + X = 1$   $1 \cdot X = X$

#### 2. Comutativas

$$X + Y = Y + X$$

$X \cdot Y = Y \cdot X$

#### 3. Associativas

$$X+(Y+Z) = (X+Y)+Z$$

$X.(Y . Z) = (X . Y).Z$

#### 4. Distributivas

$$(X + Y).(Z + W) = X.Z + X.W + Y.Z + Y.W$$

## 5. Idempotência

$$X + X = X$$

$X \cdot X = X$

# 6. Complementares

$$X + \overline{X} = 1$$

$X \cdot \overline{X} = 0$

# 7. Absorção

$$X + X.Y = X$$

$$X(X + Y) = X$$

$$X + X.Y = X$$

e  $X(X + Y) = X$  e  $X + XY = X + Y$

# 8. Inversão ou Teorema de Morgan

$$\overline{(X+Y)} = \overline{X} \cdot \overline{Y}$$

$$(\overline{X+Y}) = \overline{X} \cdot \overline{Y}$$

e  $(\overline{X} \cdot \overline{Y}) = \overline{X} + \overline{Y}$

# 9. Involução

$$=$$

$X = X$

# 10. Adjacência

$$X \cdot Y + X \cdot Y = X$$

#### 11. Dualidade

Uma relação booleana pode ser transformada na sua dual da seguinte maneira:

- \* Troca-se OR por AND e vice-versa e

- \* Troca-se 0 por 1 e vice-versa.

$$X + 0 = X$$

$$X.1 = X$$

$$X + X = 1$$

$$X \cdot X = 0$$

$$X + Y = Y + X$$

$$X \cdot Y = Y \cdot X$$

$$X + XY = X$$

$$\mathbf{X} \cdot (\mathbf{X} + \mathbf{Y}) = \mathbf{X}$$

$$\overline{X} + \overline{Y} = X \cdot Y$$

$\overline{X} \cdot \overline{Y} = \overline{X} + \overline{Y}$

$$\overline{\mathbf{X} \cdot \mathbf{Y}} = \overline{\mathbf{X}} + \overline{\mathbf{Y}}$$

$$X + X Y = X + Y$$

$$X.(X + Y) = X . Y$$

que relações ou expressões lógicas duais não são, necessariamente, equivalentes do ponto de vista lógico!

Exemplos & Aplicações:

# Exemplo 1:

Aplicar o teorema de De Morgan à função:

$$\mathbf{F} = \mathbf{A}.\mathbf{B}.\mathbf{C} + \mathbf{A}.\mathbf{B} + \mathbf{A}.\mathbf{B}.\mathbf{C}$$

1º Passo: Negar a função:

$$F = A.B.C + A.B + A.B.C$$

2º Passo: Trocar operadores externos e negar as variáveis

$$\overline{F} = (A.\overline{B}.C) \cdot (\overline{A}.B) \cdot (\overline{A}.\overline{B}.C)$$

3º Passo: Trocar operadores internos e negar variáveis internas

$$F = (A+B+C) \cdot (A+B) \cdot (A+B+C)$$

$\mathbf{4^0}$  Passo: Complementar a função  $\mathbf{F}$ , revertendo-se à função  $\mathbf{F}$  (verdadeira)

=

$$F = (A+B+C) \cdot (A+B) \cdot (A+B+C) = F$$

Pode-se observar que a aplicação do teorema de De Morgan permitiu a obtenção da mesma função lógica, através de diferentes operadores!

Tais manipulações algébricas podem vir a ser extremamente útil na implementação de circuitos lógicos, como será mostrado oportunamente!!

36

## Exemplo 2:

Projetar um circuito a relés para implementar a função:

$$F = A.(B + C) + B.(C + D.E)$$

### Solução:

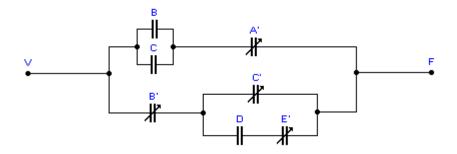

Aplicando-se os circuitos equivalentes, identificados anteriormente, para implementar as funções **AND** e **OR**, observa-se que a equação proposta representa dois ramos em paralelo. Um deles está descrito por  $\overline{\mathbf{A}}(\mathbf{B}+\mathbf{C})$ , o que corresponde ao contato  $\mathbf{A}$  em série com dois contatos em paralelo definidos por  $(\mathbf{B}+\mathbf{C})$ . Aplicando-se as mesmas considerações para o outro ramo, tem-se o circuito abaixo como resultado:

### Exemplo 3:

Escrever a expressão lógica para o circuito abaixo, simplificar a expressão resultante e esboçar o circuito equivalente:

#### Solução:

Considerando-se todos os ramos e caminhos, sejam de contatos em série ou em paralelo, para que o estado lógico presente em **V** seja comunicado ao ponto **F**, pode-se escrever:

$$F = A.B + A.C.B + A.C.D + C.D + C.B + C.C.B$$

$$= A.B + B.(A.C+C) + A.C.D + C.D$$

$$= A.B + B.(A + C) + A.C.D + C.D$$

$$= A.B + A.B + B.C + A.C.D + C.D$$

$$= A.(B + B) + B.C + A.C.D + C.D$$

$$= A + B.C + A.C.D + C.D$$

$$= A + B.C + A.C.D + C.D$$

$$= A + B.C + C.D + A.D$$

$$= A + B.C + C.D + A.D$$

$$= A.(1 + D) + C.(B + D) \quad \text{ou} \quad F = A + C.(B+D)$$

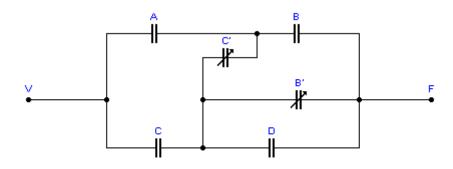

Pelo resultado acima, o circuito equivalente pode ser representado por:

Comparando-se os dois circuitos, chega-se à conclusão de que esta segunda versão possui apenas 4 contatos de relés, em lugar de 6, conforme o circuito anterior. Isto demonstra que a manipulação algébrica de uma dada equação lógica pode promover maior economia na implementação da função final.

## Exemplo 4:

Provar que X + X = X + Y. Sabe-se que:

$$X + Y = (X + Y) \cdot (X + X)$$

logo,

$= X \cdot X + X \cdot X + X \cdot Y + X \cdot Y$

$= X + X \cdot Y + X \cdot Y$  ou

$= X + X \cdot Y + X \cdot Y$

$= X \cdot (1 + Y) + X \cdot Y = X + X \cdot Y$  c.q.d.

## Exemplo 5:

Mostrar que

$$X.Y + Y.Z + X.Z = X.Y + Y.Z$$

Sabe-se que:

$$X.Y + \overline{Y}.Z = X.Y.(1 + Z) + \overline{Y}.Z.(1 + X)$$

=  $X.Y + X.Y.Z + \overline{Y}.Z + X.\overline{Y}.Z$

=  $X.Y + \overline{Y}.Z + X.Z.(Y + \overline{Y})$

=  $X.Y + \overline{Y}.Z + X.Z$  c.q.d.

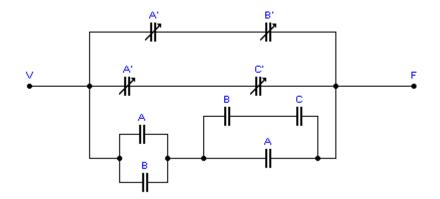

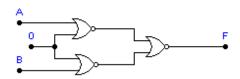

### Exemplo 6:

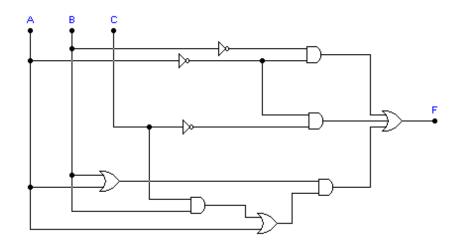

Simplificar a função descrita pelas seguintes alternativas de circuitos, cujos diagramas são apresentados tanto sob a forma de relés quanto sob a forma de portas lógicas integradas:

A alternativa do circuito acima, em diagrama de circuitos lógicos integrados, seria:

A partir de qualquer um dos circuitos acima, chega-se à seguinte equação lógica:

$$F = (A + B) \cdot (A + B \cdot C) + \overline{A} \cdot \overline{B} + \overline{A} \cdot \overline{C}$$

Aplicando-se inicialmente a propriedade distributiva da Álgebra booleana, e logo após diversas outras propriedades indicadas anteriormente, tem-se:

$$= A.A + A.B.C + A.B + B.B.C + A.B + A.C$$

$$= A + A.B.C + A.B + B.C + A.B + A.C$$

$$= A + A.B.C + A.B + B.C + A.B + A.C$$

$$= A.(1 + B.C + B) + B.C + A.B + A.C$$

$$= A + A.B + A.C + B.C$$

$$= A + \overline{B} + \overline{A}.\overline{C} + B.C = A + \overline{A}.\overline{C} + \overline{B} + B.C$$

$$= A + \overline{C} + \overline{B} + C$$

$$= A + \overline{B} + \overline{C} + C$$

$$= A + \overline{B} + \overline{C} + C$$

$$= A + \overline{B} + 1 = 1.$$

Ou seja: A função resultante equivale ao nível lógico 1.

Como deve ser interpretado este resultado?

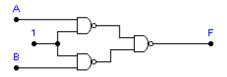

### Exemplo 7:

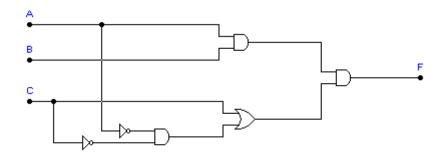

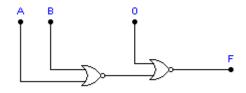

Utilizando a simbologia dos circuitos integrados para representar as portas lógicas, esboçar o diagrama que corresponde à função:

$$\mathbf{F} = \mathbf{A.B} (\mathbf{C} + \mathbf{A.C})$$

## Solução:

Existe um circuito equivalente mais simples?

### Solução:

$$F = A.B.(C + \overrightarrow{A.C}) = A.B.C + A.B.\overrightarrow{A.C}$$

$$= A.B.C + A.\overrightarrow{A.B.C} = A.B.C + 0$$

$$= A.B.C$$

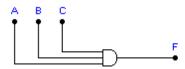

Ou seja, existe um circuito mais simples, constituído apenas por uma porta lógica **AND**, com três entradas:

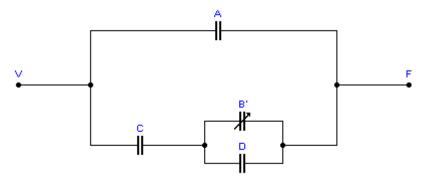

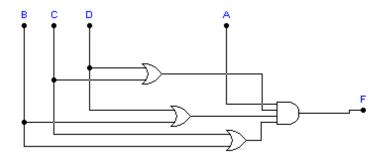

## Exemplo 8:

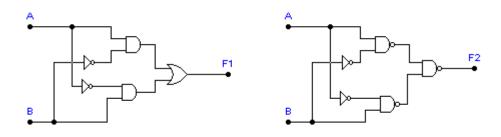

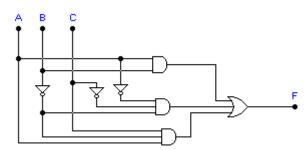

Escrever as equações lógicas que descrevem o funcionamento dos circuitos a seguir e, através da Álgebra, provar que os mesmos são equivalentes!

# Solução:

Por inspeção, vê-se que

$$F_1 = A.\overline{B} + \overline{A}.B$$

e  $F_2 = (A.\overline{B}) \cdot (\overline{A}.B).$

Ainda, noutra alternativa de notação,

$$F_1 = A.B' + A'.B$$

e  $F_2 = ((A.B')'.(A'.B)')'.$

Aplicando-se o teorema de De Morgan à função F<sub>1</sub>,

$$\overline{F}_1 = A.\overline{B} + \overline{A}.B$$

=  $\overline{F}_1 = (A.\overline{B}) \cdot (\overline{A}.B)$

Daí,

=

$$\overline{F_1} = \overline{F_1} = (A.B) \cdot (A.B) = F_2.$$

Conclusão: Os circuitos são equivalentes.

## Exemplo 9:

Prova de equivalência entre funções através de "Tabelas Verdade".

Provar que:

$$C + A.C = A + C$$

Para a comprovação da igualdade acima, pode-se construir uma tabela verdade como a mostrada abaixo, contendo as expressões de interesse.

|     |     | _   | <del></del> |

|-----|-----|-----|-------------|

| A C | A+C | A.C | C+AC        |

| 0 0 | 0   | 0   | 0           |

| 0 1 | 1   | 0   | 1           |

| 1 0 | 1   | 1   | 1           |

| 1 1 | 1   | 0   | 1           |

Por inspeção, observa-se que as colunas relativas a (C + A.C) e (A + C) são equivalentes, comprovando-se portanto a equivalência entre as funções.

# 2.4 PROPRIEDADES DAS FUNÇÕES "NAND"

a)

$$A.B.C = B.A.C = C.B.A$$

b)

$$(A.B).C \neq A.(B.C)$$

## 2.4.1 Expressões que envolvem apenas "NAND'S".

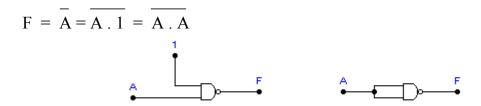

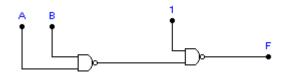

### **1. NOT**

## **2. AND**

$$F = A.B = \overline{A.B}$$

### 3. OR

$$= F = \overline{A + B} \quad F = \overline{(A \cdot 1) \cdot (B \cdot 1)}$$

# 2.5 PROPRIEDADES DAS FUNÇÕES "NOR"

a)

$$\overline{A + B + C} = \overline{B + A + C} = \overline{C + B + A} = ...$$

b)

$$\overline{A + B} + C \neq A + \overline{B + C} \neq ...$$

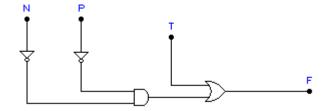

# 2.5.1 Expressões que envolvem apenas "NOR'S".

## **1. NOT**

$$F = \overline{A} = \overline{A+0} = \overline{A+A}$$

## **2. AND**

$$F = A.B$$

$F = \overline{A.B} = \overline{A} + \overline{B}$

### 3. OR

$$F = A + B = \overline{A + B}$$

## 2.6 PROPRIEDADES DAS FUNÇÕES "XOR" E "XNOR"

As funções **XOR** e **XNOR** apresentam algumas propriedades, mostradas abaixo, as quais facilitam a implementação dos circuitos lógicos:

| $X \oplus Y$                  | X O Y                         |

|-------------------------------|-------------------------------|

| $0 \oplus 0 = 0$              | 0 • 0 = 1                     |

| $0 \oplus 1 = 1$              | 0 • 1 = 0                     |

| $1 \oplus 0 = 1$              | 1 • 0 = 0                     |

| 1 ⊕ 1 = 0                     | 1 • 1 = 1                     |

| $0 \oplus X = X$              | 0 ⊙ X = X'                    |

| $1 \oplus X = X'$             | 1 <b>③</b> X = X              |

| X'⊕ X = 1                     | X' ⊙ X = 0                    |

| $X \oplus X = 0$              | X ⊙ X = 1                     |

| $X' \oplus Y = X \odot Y$     | $X' \odot Y = X \oplus Y$     |

| $X \oplus Y' = X \odot Y$     | $X \odot Y' = X \oplus Y$     |

| $(X \oplus Y)' = X \odot Y$   | $(X \odot Y)' = X \oplus Y$   |

| $X \oplus Y \oplus X.Y = X+Y$ | $X \odot Y \odot X.Y = X + Y$ |

| $X \oplus X.Y = X.Y$          | $X \odot X.Y = (X.Y')'$       |

| $X \oplus (X + Y) = X'.Y$     | $X \odot (X+Y) = (X'.Y)'$     |

| $X \oplus X'.Y = X + Y$       | $X \odot X'.Y = (X + Y)'$     |

| $X \oplus (X'+Y)=(X.Y)'$      | X <b>⊙</b> (X'+Y)=X.Y         |

Recomenda-se, como exercício, a demonstração algébrica das relações do quadro acima, onde as variáveis negadas estão representadas por X', Y', (X + Y)', etc.

Devido à grande vantagem da aplicação do OR exclusivo ou da Coincidência na implementação dos circuitos lógicos, deve-se sempre procurar verificar se existe a possibilidade de se expressar equações lógicas mais complexas, através desses operadores. Vale observar que existem circuitos integrados que efetuam as operações **XOR** e **XNOR** diretamente.

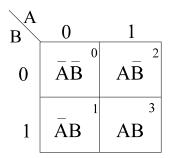

### 2.7 FORMAS CANÔNICAS

As expressões booleanas, envolvendo os diversos operadores, podem ser escritas na sua forma canônica, seja em soma de produtos (**S.O.P.**) ou em produto de somas (**P.O.S.**).

A vantagem de se exprimir uma função booleana nessa forma reside no fato desse tipo de expressão permitir a representação numérica da função, facilitando assim os procedimentos de simplificação.

As reduções ou simplificações sistemáticas das funções, sobretudo através dos mapas de Karnaugh e do método Quine McCluskey, se baseiam nas formas canônicas das funções a serem simplificadas. Esses procedimentos permitem maior independência de artificios algébricos, e facilitam a identificação da expressão mais simples para representar a mesma função lógica.

Uma função **F**(**A,B,C**<sub>1</sub>) escrita em **S.O.P**. ou **P.O.S**. tem a forma geral abaixo:

$$\triangleright$$

S.O.P.  $F(A,B,C) = (A.B.C) + (A.B.C) + ...$

ou

$$ightharpoonup P.O.S F(A,B,C) = (A + B + C) ... (A + B + C) ...$$

Quando cada termo da expressão em **S.O.P.** ou **P.O.S.** contém todas as variáveis da função, diz-se que a mesma encontra-se escrita sob a forma **standard** ou **completa**.

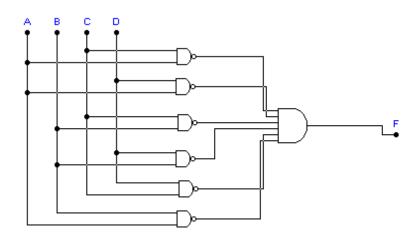

#### 2.7.1 Funções em S.O.P.

A função

$$F(A.B.C.D) = A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D$$

encontra-se escrita sob a forma standard ou completa.

Os termos ou parcelas da expressão são denominados termos mínimos (**MINTERM's**) da função; isto porque a função é verdadeira para o número mínimo de parcelas verdadeiras presentes na expressão.

Toda **S.O.P.** completa pode ser escrita na sua representação numérica, convencionando-se:

variável falsa =

$$\mathbf{0}$$

e variável verdadeira =  $\mathbf{1}$

A partir dessa convenção, atribuem-se valores **0** ou **1** às variáveis presentes em cada Termo Mínimo (**MINTERM**), e encontra-se o decimal correspondente a cada um deles. Esses decimais definem a representação numérica da função, conforme indicado a seguir.

#### **Exemplo:**

$$F(A,B,C) = \overrightarrow{A}.\overrightarrow{B}.\overrightarrow{C} + \overrightarrow{A}.\overrightarrow{B}.\overrightarrow{C} + \overrightarrow{A}.\overrightarrow{B}.\overrightarrow{C} + \overrightarrow{A}.\overrightarrow{B}.\overrightarrow{C}$$

$$0\ 0\ 0\ 1\ 0\ 0\ 1\ 0\ 1\ 1\ 1\ 1$$

$$MINTERM's: (0) (4) (5) (7)$$

Representação numérica da função:

$$F(A,B,C) = \sum_{i=1}^{n} m(0,4,5,7)$$

É importante observar que a primeira variável (A) é a mais significativa (MSB), e a última (C), a menos significativa (LSB). Esta convenção deve ser obedecida, para que a representação numérica decimal se mantenha coerente com o seu equivalente binário.

#### **Outro exemplo:**

$$F(A,B,C,D) = \overrightarrow{A.B.C.D} + \overrightarrow{A.B.C.D} + \overrightarrow{A.B.C.D} + \overrightarrow{A.B.C.D} + \overrightarrow{A.B.C.D}$$

$$0\ 0\ 0\ 0\ 1\ 1\ 0\ 1\ 0\ 1$$

$$1\ 1\ 0\ 1$$

$$MINTERM's: (0) (3) (5) (13)$$

Tem-se então a representação numérica da função como em sendo:

$$F(A,B,C,D) = \sum m(0,3,5,13)$$

Evidentemente, quando a função está sob a forma numérica, a sua expressão algébrica pode ser encontrada pelo processo inverso.

Exemplo:

Escrever em soma de produtos a função representada por:

$$F(A,B,C,D) = \Sigma m(1,5,7,13,15)$$

Processo inverso:

Sabe-se que cada MINTERM tem os correspondentes binários indicados a seguir:

MINTERM's: (1) (5) (7) (13) (15)

Binário: 0001 0101 0111 1101 1111

logo,

A.B.C.D A.B.C.D A.B.C.D A.B.C.D A.B.C.D

ou

$$F(A.B.C.D) = A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D$$

Quando a S.O.P. encontra-se representada na forma incompleta, a sua representação numérica não é possível. Para tornar possível esta representação, a S.O.P. incompleta deve ser transformada em completa, seja através de artifícios algébricos, ou mesmo através de tabelas verdade, sem que o valor lógico da função venha a sofrer alteração.

#### Exemplo de S.O.P. incompleta:

$$F(A,B,C,D) = A.B.C$$

Vê-se que a variável "D" não está presente no único termo da função.

Para transformar tal equação em representação completa ou *standard*, deve-se incluir a variável "**D**", sem alterar o valor lógico da função.

Assim, sabendo-se que D + D = 1, e que F.1 = F, faz-se:

$$F(A,B,C,D) = \overline{A}.B.C$$

$$F(A,B,C,D) = A.B.C.(D+D)$$

$$F(A,B,C,D) = A.B.C.D + A.B.C.D$$

ou

$$F(A,B,C,D) = \sum m (8,9)$$

Um modo prático de se chegar ao mesmo resultado é exemplificado abaixo:

Seja a função incompleta:

$$F(A,B,C,D) = A.C.D$$

Como a variável " $\mathbf{B}$ " encontra-se ausente, tem-se:  $\mathbf{1} \ \mathbf{X} \ \mathbf{0} \ \mathbf{0}$  onde " $\mathbf{X}$ " representa a variável " $\mathbf{B}$ ", a qual pode assumir apenas os valores  $\mathbf{0} \ \mathbf{e} \ \mathbf{1}$ .

Assim, dois termos possíveis são:

$$1000 = 8$$

e  $1100 = 12$

Logo,  $F(A,B,C,D) = \sum m(8,12)$ , tendo como representação algébrica :

$$F(A,B,C,D) = A.B.C.D + A.B.C.D$$

Quando o número de variáveis ausentes é grande, o método mais prático para se encontrar a função completa, e a correspondente representação numérica, é o da tabela verdade como se mostra a seguir:

Seja:

$$F(A,B,C,D,E) = B.E$$

Vê-se que as variáveis "A", "C" e "D" estão ausentes. Assim, cria-se então a tabela-verdade conforme demonstrado abaixo, fazendo-se constar todas as configurações binárias possíveis para tais variáveis e, na coluna seguinte, acrescentam-se as variáveis presentes, atribuíndo-se os valores lógicos pertinentes. Os decimais equivalentes às configurações completas, definem os MINTERM's da função.

| Variáveis | Termos                  | Decimais     |

|-----------|-------------------------|--------------|

| Ausentes  | Completos               | Equivalentes |

| ACD       | ABCDE                   | MINTERMS     |

| 0 0 0     | 00001                   | 1            |

| 0 0 1     | 00011                   | 3            |

| 0 1 0     | 0 <b>0</b> 1 0 <b>1</b> | 5            |

| 0 1 1     | 0 <b>0</b> 1 1 <b>1</b> | 7            |

| 1 0 0     | 1 <b>0</b> 0 0 <b>1</b> | 17           |

| 1 0 1     | 1 0 0 1 1               | 19           |

| 110       | 1 <b>0</b> 1 0 <b>1</b> | 21           |

| 111       | 10111                   | 23           |

ou seja,  $F(A,B,C,D,E) = \sum_{i=0}^{\infty} m(1,3,5,7,17,19,21,23).$

#### 2.7.2 Funções em P.O.S.

A função abaixo encontra-se escrita sob a forma completa, em Produtos de Somas (P.O.S.):

$$F(A.B.C.D) = (A+B+C+D).(A+B+C+D).(A+B+C+D).(A+B+C+D)$$

Os termos ou parcelas da expressão são denominados Termos Máximos (**MAXTERMS**) da função; isto porque a função é verdadeira para o número máximo de parcelas verdadeiras, presentes na expressão!

Todo **P.O.S.** completo pode ser escrito na sua representação numérica, segundo a convenção usada anteriormente. Contudo, o procedimento para se encontrar a representação numérica de um **P.O.S.** requer que se encontre o complemento de cada uma das variáveis, antes de se encontrar o decimal equivalente, como indicado a seguir:

$$F(A,B,C,D) = (A+B+C+D).(A+B+C+D).(A+B+C+D).(A+B+C+D).$$

COMPLEMENTOS: (0 1 0 1).(1 0 0 0).(0 0 1 1).(1 0 0 1)

Daí, ordenando em ordem crescente,  $F(A,B,C,D) = \prod M(3,5,8,9)$ .

Onde  $\Pi$  representa o produto dos Termos Máximos da função.

Outro exemplo:

$$\mathbf{F}(\mathbf{W},\mathbf{X},\mathbf{Y},\mathbf{Z}) = (\mathbf{W} + \mathbf{X} + \mathbf{Y} + \mathbf{Z})$$

COMPLEMENTOS: 1 0 0 1

MAXTERM: 9

Ou seja:  $F(W,X,Y,Z) = \prod M(9)$

Também, como no caso da **S.O.P.**, pode-se escrever a expressão algébrica do **P.O.S.** a partir da representação numérica, lembrando-se de encontrar o complemento antes de se reverter à variável original, como nos exemplos abaixo:

Escrever em **P.O.S.** a função:

#### **COMPLEMENTOS:**

$$F = (A+B+C+D).(A+B+C+D).(A+B+C+D).(A+B+C+D)$$

Quando a função está expressa sob a forma incompleta, procede-se de modo similar ao caso da S.O.P., conforme os exemplos:

### Exemplo 1:

$$F(A,B,C,D) = (A+C+D).(A+B)$$

F1 . F2

Pela expressão F1,

$$F1 = A+C+D+(B.B)$$

$$F1 = (A+C+D+B).(A+C+D+B)$$

$$F1 = (A+B+C+D).(A+B+C+D).$$

Do mesmo modo,

$$F2 = A + B + (C.C) + (D.D)$$

$$F2 = (A + B + C).(A + B + C) + (D.D)$$

$$F2 = (A + B + C + D).(A + B + C + D).(A + B + C + D)$$

ou seja,

$$F(A,B,C,D) = F1 \cdot F2$$

ou

$F(A,B,C,D) =$

$$= (A+B+C+D) \cdot (A+B+C+D) \cdot (A+B+C+D) \cdot (A+B+C+D)$$

### Exemplo 2:

Encontrar a representação numérica do P.O.S.

$$F(W,X,Y,Z) = (W+Y).(W+Y+Z).(X+Y+Z)$$

Considerando-se todos os valores lógicos possíveis para as variáveis ausentes em cada termo, tem-se:

$$\overline{W}+Y : \Rightarrow [1+X+0+Z] \Rightarrow \{8,9,12,13\}$$

$$\overline{W}+Y+Z : \Rightarrow [0+X+1+0] \Rightarrow \{2,6\}$$

$$\overline{X}+Y+Z : \Rightarrow [W+0+0+1] \Rightarrow \{1,9\}$$

$$F(W,X,Y,Z) = \prod M (1,2,6,8,9,12,13)$$

### Exemplo 3:

$$F(A,B,C,D) = A + \overline{C}$$

Pelo método da tabela-verdade:

| BD  | ABC'D                 | MINTERM |

|-----|-----------------------|---------|

| 0 0 | 0010                  | 2       |

| 0 1 | <b>0</b> 0 <b>1</b> 1 | 3       |

| 1 0 | <b>0</b> 1 <b>1</b> 0 | 6       |

| 11  | <b>0</b> 1 <b>1</b> 1 | 7       |

↑ ↑ Complementos !:

Pelos termos mínimos resultantes tem-se

$$F(A,B,C,D) = \Pi M (2,3,6,7)$$

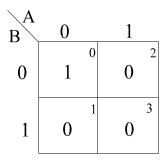

### 2.8 Relação entre P.O.S. / S.O.P. e Tabelas-Verdade

Seja a tabela verdade da função XOR abaixo:

| DEC | A B | F |

|-----|-----|---|

| 0   | 0 0 | 0 |

| 1   | 0 1 | 1 |

| 2   | 1 0 | 1 |

| 3   | 1 1 | 0 |

Como nos casos anteriores, a tabela-verdade especifica a função F como sendo verdadeira para as situações definidas pela equação:

$$F(A,B) = A.B + A.B$$

, cuja representação numérica é:

Binário 0 1 1 0

MINTERM's 1 2 ou

$$F(A,B) = A.B + A.B = \sum_{i=1}^{n} m(1,2).$$

A mesma tabela-verdade especifica a função  ${\bf F}$  como falsa para as situações definidas por:

$$\overline{F(A,B)} = \overline{A.B} + A.B.$$

Aplicando-se o teorema de De Morgan à expressão acima tem-se:

$$\overline{F(A,B)} = \overline{A}.\overline{B} + A.B$$

ou

$$F(A,B) = (\overline{A}.\overline{B}) \cdot (A.B)$$

$$F(A,B) = (A+B) \cdot (A+B)$$

.

Esta última expressão é a representação da função sob a forma de P.O.S.! Encontrando-se a sua representação numérica, tem-se:

$$F(A.B) = (A+B).(A+B)$$

Complemento 0 0 . 1 1

MAXTERM's 0

ou

$$F(A,B) = (A+B).(A+B) = \prod M (0,3).$$

Observa-se, entretanto, que a expressão F(A,B) = (A+B).(A+B) pode ser desenvolvida algebricamente do seguinte modo, a partir da propriedade distributiva:

$$F(A,B) = (A+B).(A+B) = A.A + A.B + A.B + B.B$$

$$= 0 + A.B + A.B + 0.$$

Daí,

$$F(A,B) = (A+B).(A+B) = A.B + A.B.$$

Ou seja:

$$F(A,B) = \prod M(0,3) = \sum m(1,2).$$

Isto significa que a expressão definida a partir da função verdadeira, em S.O.P., é equivalente à definida a partir da função falsa, em P.O.S.

Logo, tanto faz se exprimir uma mesma função a partir dos 1's em S.O.P., quanto a partir dos 0's em P.O.S.

Vale dizer que as expressões são equivalentes entre sí, podendo uma delas ser transformada na outra, através da aplicação do teorema de De Morgan e outras propriedades algébricas!

Observa-se ainda que os números decimais que não constam da **S.O.P**. são os que definem o **P.O.S**. e vice-versa. Isto porque, quando todas as configurações entre as variáveis são examinadas e definem os valores lógicos de determinada função, os termos que não são **1's**, necessariamente serão **0's** e vice-versa. Ou seja, o que não corresponde a termo mínimo (**MINTERM**) é, necessariamente, termo máximo (**MAXTERM**) da função.

### **Outro exemplo:**

- Seja a função F(X,Y,Z) definida pela tabela verdade a seguir:

| DEC | XYZ   | F |

|-----|-------|---|

| 0   | 0 0 0 | 1 |

| 1   | 0 0 1 | 0 |

| 2   | 0 1 0 | 1 |

| 3   | 0 1 1 | 0 |

| 4   | 100   | 1 |

| 5   | 1 0 1 | 1 |

| 6   | 1 1 0 | 0 |

| 7   | 111   | 1 |

Provar que as expressões em **S.O.P** e **P.O.S.** da função, assim definida, são equivalentes entre sí.

#### Solução:

A tabela-verdade indica as expressões em S.O.P. e P.O..S., respectivamente:

$$F(X,Y,Z)_{SOP} = \sum m(0,2,4,5,7)$$

e  $F(X,Y,Z)_{POS} = \prod M(1,3,6)$

Partindo-se da primeira expressão, pode-se escrever que:

$$F(X,Y,Z) = \sum m(0,2,4,5,7)$$

$$F(X,Y,Z)_{SOP} = X.Y.Z + X.Y.Z + X.Y.Z + X.Y.Z + X.Y.Z + X.Y.Z$$

$$F(X,Y,Z)_{SOP} = X.Y.Z + X.Y.Z + X.Y.Z + (X.Y.Z + X.Y.Z) + X.Y.Z$$

$$= XZ.(Y+Y) + X.Y(Z+Z) + X.Z(Y+Y)$$

$$= X.Z + X.Y + X.Z$$

$$\mathbf{F}(\mathbf{X},\mathbf{Y},\mathbf{Z})_{SOP} = \mathbf{X}.\mathbf{Z} + \mathbf{X}.\mathbf{Y} + \mathbf{X}.\mathbf{Z}$$

$F(X,Y,Z)_{POS} = X.Z + X.Y + X.Z$

Da mesma maneira,

$$F(X,Y,Z)_{POS} = (X+Y+Z).(X+Y+Z).(X+Y+Z)$$

$$= (X+Z).(Y+Y).(X+Y+Z)$$

$$= (X+Z).(X+Y+Z)$$

$$= (X+Z).(X+Y+Z)$$

$$= X.X + X.Y + X.Z + X.Z + Y.Z + Z.Z$$

$$= X.Y + X.Z + Y.Z + X.Z$$

$$= (X.Y + X.Z) + X.Z$$

Pode-se observar, então, que as expressões em **S.O.P**. e **P.O.S** resultam na mesma equação lógica, provando-se a equivalência entre as mesmas.

Exercício:

Seja a função definida pela tabela verdade abaixo:

| DEC | ABCD    | F |

|-----|---------|---|

| 0   | 0000    | 0 |

| 1   | 0 0 0 1 | 0 |

| 2   | 0010    | 0 |

| 3   | 0 0 1 1 | 0 |

| 4   | 0 1 0 0 | 0 |

| 5   | 0 1 0 1 | 1 |

| 6   | 0110    | 0 |

| 7   | 0 1 1 1 | 1 |

| 8   | 1000    | 0 |

| 9   | 1001    | 0 |

| 10  | 1010    | 0 |

| 11  | 1011    | 0 |

| 12  | 1100    | 0 |

| 13  | 1101    | 1 |

| 14  | 1110    | 0 |

| 15  | 1111    | 1 |

A função é verdadeira para:

S.O.P.

A partir dos zeros tem-se:

P.O.S.  $F(A,B,C,D) = \prod_{i=1}^{n} M(0,1,2,3,4,6,8,9,10,11,12,14)$

Como exercício, provar que as expressões em **S.O.P** e **P.O.S**. são equivalentes. Apenas para fixar idéias, apresenta-se o quadro a seguir, para uma função F(A,B,C,D), onde especificam-se os valores lógicos e as formas de representar os MINTERM's e os MAXTERM's de uma função de quatro variáveis:

| DEC | A B C D | F | MINTERMS                                                                                        | MAXTERMS                                                                                        |

|-----|---------|---|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 0   | 0 0 0 0 | 0 | $\overline{\mathbf{A}} \ \overline{\mathbf{B}} \ \overline{\mathbf{C}} \ \overline{\mathbf{D}}$ | A+B+C+D                                                                                         |

| 1   | 0 0 0 1 | 0 | $\overline{\mathbf{A}} \ \overline{\mathbf{B}} \ \overline{\mathbf{C}} \ \mathbf{D}$            | $\mathbf{A} + \mathbf{B} + \mathbf{C} + \overline{\mathbf{D}}$                                  |

| 2   | 0010    | 1 | $\overline{\mathbf{A}} \ \overline{\mathbf{B}} \ \mathbf{C} \ \overline{\mathbf{D}}$            | $\mathbf{A} + \mathbf{B} + \overline{\mathbf{C}} + \mathbf{D}$                                  |

| 3   | 0 0 1 1 | 1 | $\overline{\mathbf{A}} \ \overline{\mathbf{B}} \ \mathbf{C} \ \mathbf{D}$                       | $A+B+\overline{C}+\overline{D}$                                                                 |

| 4   | 0100    | 1 | $\overline{\mathbf{A}} \mathbf{B} \overline{\mathbf{C}} \overline{\mathbf{D}}$                  | $\mathbf{A} + \overline{\mathbf{B}} + \mathbf{C} + \mathbf{D}$                                  |

| 5   | 0 1 0 1 | 0 | $\overline{\mathbf{A}} \mathbf{B} \overline{\mathbf{C}} \mathbf{D}$                             | $\mathbf{A} + \overline{\mathbf{B}} + \mathbf{C} + \overline{\mathbf{D}}$                       |

| 6   | 0110    | 1 | A B C D                                                                                         | $\mathbf{A} + \overline{\mathbf{B}} + \overline{\mathbf{C}} + \mathbf{D}$                       |

| 7   | 0 1 1 1 | 0 | A B C D                                                                                         | $\mathbf{A} + \overline{\mathbf{B}} + \overline{\mathbf{C}} + \overline{\mathbf{D}}$            |

| 8   | 1000    | 0 | A B C D                                                                                         | $\overline{\mathbf{A}} + \mathbf{B} + \mathbf{C} + \mathbf{D}$                                  |

| 9   | 1 0 0 1 | 0 | $A \overline{B} \overline{C} D$                                                                 | $\overline{\mathbf{A}} + \mathbf{B} + \mathbf{C} + \overline{\mathbf{D}}$                       |

| 10  | 1010    | 1 | $A \overline{B} C \overline{D}$                                                                 | $\overline{\mathbf{A}} + \mathbf{B} + \overline{\mathbf{C}} + \mathbf{D}$                       |

| 11  | 1011    | 1 | $A \overline{B} C D$                                                                            | $\overline{\mathbf{A}} + \mathbf{B} + \overline{\mathbf{C}} + \overline{\mathbf{D}}$            |

| 12  | 1100    | 0 | A B C D                                                                                         | $\overline{\mathbf{A}} + \overline{\mathbf{B}} + \mathbf{C} + \mathbf{D}$                       |

| 13  | 1 1 0 1 | 1 | A B C D                                                                                         | $\overline{\mathbf{A}} + \overline{\mathbf{B}} + \mathbf{C} + \overline{\mathbf{D}}$            |

| 14  | 1110    | 0 | A B C D                                                                                         | $\overline{\mathbf{A}} + \overline{\mathbf{B}} + \overline{\mathbf{C}} + \mathbf{D}$            |

| 15  | 1111    | 0 | A B C D                                                                                         | $\overline{\mathbf{A}} + \overline{\mathbf{B}} + \overline{\mathbf{C}} + \overline{\mathbf{D}}$ |

A função "F" definida como acima será representada por:

$$F(A,B,C,D) = \sum m(2,3,4,6,10,11,13) = \prod M (0,1,5,7,8,9,12,14,15), \text{ ou seja:}$$

$$F = A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D$$

$$F(A,B,C,D) = \prod M (0,1,5,7,8,9,12,14,15).$$

Ou seja:

$$F(A,B,C,D) = (A+B+C+D).(A+B+C+D).(A+B+C+D).$$

$$(A+B+C+D).(A+B+C+D).(A+B+C+D).$$

$$(A+B+C+D).(A+B+C+D).(A+B+C+D).$$

Através de manipulações algébricas, conforme procedimentos anteriormente mostrados, pode-se provar que as expressões em S.O.P e P.O.S são equivalentes; ou seja:

$$F(A,B,C,D) = \sum m(2,3,4,6,10,11,13) = \prod M(0,1,5,7,8,9,12,14,15)$$

Observa-se, mais uma vez, que os decimais ausentes na representação em MINTERM's são os que constam da representação em MAXTERM's.