# UFEEJ4-40-3 - Individual Project (CRTS)

| Student:            | Edwin Langley 02503280                        |

|---------------------|-----------------------------------------------|

| Project supervisor: | Craig Duffy                                   |

| Second reader:      | Nigel Gunton                                  |

| Award title:        | BSc Computing for Real Time Systems           |

| Project title:      | uClinux on the Pluto 6 embedded control board |

| Word count:         | 16500                                         |

## **Synopsis**

This project is based around a control board known as the Pluto 6, produced by a company called Heber Ltd. The aim of the project was to port an operating system to the Pluto 6 board. Following a successful port, drivers were to be written for some of the custom hardware on the board.

The design techniques used to develop the drivers for the project depended on the level of interaction required with the rest of the kernel. The frame buffer driver written was a bottom-up design. The operation of the hardware, and the behaviour expected by the rest of the kernel was known, so algorithms were then designed to bridge the gap between these layers until the video card was utilised correctly by the kernel. Conversely, the VFD and multiplexed lamp drivers were a top-down design. These drivers had no major subsystem, allowing flexibility. The interface required by user programs was first defined, and the code to drive the hardware designed accordingly.

The programming language used throughout was C, except for the kernel entry code, which was GNU 68K assembly. The equipment used in the project, aside from the board itself, was a P&E BDM debugging module, CompactFlash card reader, and serial cable. These components were used with an X86 development host running Linux.

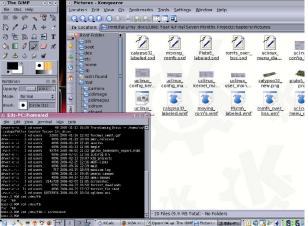

The progress made on the project was good, the kernel was ported to the board and made to execute in place, and drivers written for the Vacuum Fluorescent Display (VFD), multiplexed lamps and graphics frame buffer. The Integrated Drive Electronics (IDE) interface was enabled by editing a driver provided in uClinux. The result is that the Pluto 6 will boot into uClinux at power on, and can then run programs from the root file system mounted on the CompactFlash card, including the Nano-X server running through the frame buffer device.

Although time didn't allow writing drivers for all of the devices suggested, such as the I2C, the three main areas desired were achieved – that is the kernel port , a frame buffer graphics driver with X and the IDE interface. The project can therefore be considered successful.

# **Table of Contents**

| 1 Introduction                                              | 6   |

|-------------------------------------------------------------|-----|

| 1.1 Project origin                                          | 6   |

| 1.1.1 The current software system                           | 6   |

| 1.1.1.1 Advantages                                          | 6   |

| 1.1.1.2 Disadvantages                                       | 6   |

| 1.1.2 The problem                                           | 7   |

| 1.1.3 The solution                                          | 7   |

| 1.2 Choosing an OS                                          | 7   |

| 1.3 Requirements                                            |     |

| 1.4 Project life cycle                                      |     |

| 2 The Pluto 6 board and the current system                  |     |

| 2.1 ColdFire CPU background                                 |     |

| 2.2 Further Pluto 6 information                             |     |

| 2.3 Current software system                                 |     |

| 3 uClinux                                                   |     |

| 3.1 Overview                                                |     |

| 3.2 History                                                 |     |

| 3.3 Differences to the normal kernel                        | 19  |

| 3.3.1 The role of the Memory management Unit                | 19  |

| 3.3.1.1 Virtual memory                                      | 20  |

| 3.3.1.2 Protection.                                         |     |

| 3.3.2 Running an OS without a MMU                           |     |

| 3.3.3 Other differences                                     |     |

| 3.4 Summary                                                 |     |

| 4 Porting uClinux to the Pluto 6                            |     |

| 4.1 Linux kernel boot sequence                              |     |

| 4.1.1 After assembly.                                       |     |

| 4.2 Design                                                  |     |

| 4.2.1 Kernel version                                        |     |

| 4.2.2 Kernel location options                               |     |

| 4.3 Implementation.                                         |     |

| 4.3.1 Setting up a development environment                  |     |

| 4.3.1.1 Testing the development environment                 |     |

| 4.3.2 Creating the initial port.                            |     |

| 4.3.2.1 Entry assembly                                      |     |

| 4.3.2.2 Linker description file                             |     |

| 4.3.3 Running the kernel.                                   |     |

| 4.3.4 Getting more memory                                   |     |

| 4.3.5 Execute in place                                      |     |

| 4.4 Testing.                                                |     |

| 5 The Frame buffer driver                                   |     |

| 5.1 Introduction.                                           |     |

|                                                             |     |

| 5.2 History<br>5.3 Graphics controller capabilities         | 54  |

|                                                             |     |

| 5.4 About the Linux frame buffer subsystem                  |     |

| 5.4.1 Origin                                                |     |

| 5.4.2 In user space                                         |     |

| 5.4.3 In kernel space                                       |     |

| 5.5 The Fujitsu Cremson graphics controller                 |     |

| 5.6 Implementing a Linux frame buffer driver on the Cremson |     |

| 5.6.1 Design                                                | .08 |

| 5.6.2 Implementation                                           |          |

|----------------------------------------------------------------|----------|

| 5.6.2.1 16 bit mode                                            |          |

| 5.6.2.2 8 bit mode                                             |          |

| 5.6.3 Running Nano X.                                          |          |

| 5.6.3.1 16 bit mode                                            |          |

|                                                                |          |

| 5.6.3.2 8 bit mode                                             |          |

| 6 Conclusion                                                   |          |

| 6.1 Performance of the system                                  |          |

| 6.2 Further work                                               |          |

| 6.3 What has been learned                                      |          |

| 7 Bibliography                                                 |          |

| 7.1 Books                                                      |          |

| 7.2 Articles                                                   |          |

| 7.3 Papers                                                     |          |

| 7.4 Manuals                                                    |          |

| 7.5 Websites                                                   |          |

| 7.6 Mailing lists                                              |          |

| 8 Glossary                                                     |          |

| 9 Appendix A - Further ColdFire information                    |          |

| 9.1 Differences to the 68000                                   |          |

| 9.1.1 Simplified addressing modes:                             |          |

| 9.1.2 Reduced instruction set                                  |          |

| 9.1.3 Restricted instructions                                  |          |

| 9.1.4 Supervisor mode differences                              |          |

| 10 Appendix B - Further Pluto 6 information                    |          |

| 10.1 Accompanying Hardware on the Pluto 6                      | 95<br>95 |

| 10.1.1 FPGA                                                    |          |

| 10.1.2 Microchip PIC                                           |          |

| 10.1.3 CPLD.                                                   |          |

| 10.1.5 CFLD<br>10.2 Hardware Boot sequence                     |          |

|                                                                |          |

| 10.3 ColdFire configuration on the Pluto 6                     |          |

| 10.3.1 Pin assignments                                         |          |

| 10.3.2 Interrupts on the Pluto 6 board                         |          |

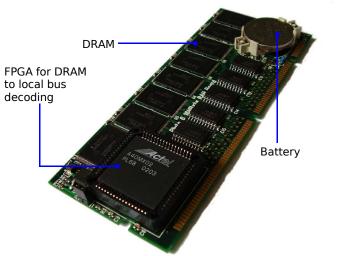

| 10.3.3 Chip selects and DRAM.                                  |          |

| 11 Appendix C – The Heber software architecture                |          |

| 11.1 Software architecture                                     |          |

| 11.2 The boot sequence                                         |          |

| 12 Appendix D - uClinux and Linux boot sequence comparison     |          |

| 12.1 Power on                                                  |          |

| 12.2 X86 PC Linux kernel boot sequence                         |          |

| 12.3 ColdFire uClinux kernel boot sequence                     |          |

| 13 Appendix E - Variations in Graphics controller capabilities |          |

| 14 Appendix F - Features of the Cremson MB86290A               |          |

| 14.1 Resolutions                                               |          |

| 14.2 Layer/frame control                                       |          |

| 14.3 2d primitives and anti-aliasing                           |          |

| 14.4 3d polygons and perspective texture mapping               |          |

| 14.5 Display lists                                             |          |

| 15 Appendix G - The multiplexed lamps and VFD drivers          |          |

| 15.1 The VFD driver                                            |          |

| 15.1.1 Design                                                  |          |

| 15.1.2 Implementation                                          |          |

| 15.2 The multiplexed lamps driver                              |          |

| 15.2.1 Design                                                  |          |

| 15.2.2 Implementation.                                         |          |

| 16 Appendix H - The CompactFlash IDE driver                    |          |

| TO APPENDIX IT - THE COMPACT IASH IDE UNVEL                    |          |

|    | 16.1 Design                            | .115 |

|----|----------------------------------------|------|

|    | 16.2 Implementation                    | .115 |

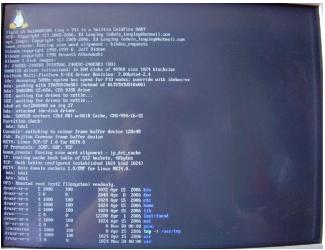

| 17 | Appendix I - The working kernel output | .117 |

|    | Appendix J - the BDM-CHK test output   |      |

| 19 | Appendix K - Source code listings.     | .124 |

|    | 19.1 crt0 ram.S                        | .124 |

|    | 19.2 ram.ld                            |      |

|    | 19.3 crt0 rom.S                        | .128 |

|    | 19.4 rom.ld                            | .135 |

|    | 19.5 gdbinit<br>19.6 vfd.c             | .136 |

|    | 19.6 vfd.c                             | .140 |

|    | 19.7 mpxlamps.c                        | .145 |

|    | 19.8 pluto6 fpga.h                     | .152 |

|    | 19.9 uclinux.c.                        | .152 |

|    | 19.10 cremsonfb.c                      | .163 |

|    | 19.11 cremsonfb.h                      |      |

|    |                                        |      |

## **1** Introduction

Heber Ltd provide control systems for the gambling machine (also known as fruit machine) industry. The Pluto 6 board is sold to fruit machine manufacturers who write the games to run on it. The board is then placed into a fruit machine cabinet and controls all of the peripherals present. The Hardware in a game cabinet can include up to two video screens, lamps, button switches, stepper motors controlling the reels in the cabinet, coin and note acceptors, VFDs and audio speakers.

## 1.1 Project origin

#### 1.1.1 The current software system

The board as supplied by Heber uses pre-compiled custom hardware libraries written from scratch inhouse, which are then linked with the game code to create a single binary. The current libraries can drive the hardware provided such as the serial ports, and even offer FAT32 support for the CompactFlash card.

#### 1.1.1.1 Advantages

The no OS approach taken has been successful, games have been written by fruit machine manufacturers and sold well. The libraries provide a high level of control over the system, due to the code being developed in house and hence well known.

#### 1.1.1.2 Disadvantages

There are however certain problems with the current software architecture.

- The project makefiles use relative paths to include the library files. Every time a new version

of a library is released, the version number in the paths of the makefile must be altered. The

hardware library path is also used in the linker script to refer to the vector table location and

this must also be altered. It soon becomes easy for a game developer to get out of sync with

the four separate libraries in both of these files, causing compilation or linking errors. It is up

to them to remember to maintain their project files.

- Since the libraries are all compiled separately before the project is compiled and linked with them, development on the libraries can become tedious, e.g. if something is changed in the hardware library, it must be recompiled, since the other libraries have dependencies on it they must be recompiled, before a project can be compiled to actually test the changes.

- The Pluto range is responsible for the majority of Hebers technical support effort. Due to the code being closed source and completely proprietary, maintaining it and removing bugs, while other engineers are continually adding features is a big undertaking.

### 1.1.2 The problem

So far the hardware in the Pluto range has not presented a significant problem as far as writing drivers from scratch is concerned. However Hebers future boards will be more powerful, possibly featuring sophisticated peripheral interfaces including USB and Ethernet. The software architecture in place may restrict future development on these new products. It is not feasible to write a TCP/IP stack from scratch for Ethernet, or a USB stack along with drivers for every plausible USB device which could be used in a fruit machine.

## 1.1.3 The solution

The increasing complexity of hardware interfaces and peripheral buses may be handled by providing support for an Operating System (OS) on future boards. Future Pluto platforms may therefore require moving to an OS as the software base. The bulk of the driver development will have been done, and a support community can aid in solving bugs.

It was therefore decided to port an OS to the current board, the Pluto 6.

## 1.2 Choosing an OS

The OS chosen was uClinux – a fork of Linux with alterations to allow it to run on low cost micro controllers with no memory management unit. UClinux was used for the following reasons:

- The CPU on the board is a Motorola ColdFire, which has no MMU. UClinux is designed for exactly this level of micro controller, hence the ColdFire range is one of the architectures most strongly supported the operating system.

- UClinux is similar enough to Linux that the knowledge gained from writing drivers for the project would be useful for many other systems running a Linux port. This was the main deterrent from using one of the numerous real time executives available for the ColdFire, such as FreeRTOS or VxWorks.

- UClinux is open source, so it can be fully debugged. Access to the source code is also important in order to make sufficient alterations kernel for it to run on the board with the right memory map.

- UClinux is free.

- UClinux has a strong community support base, due to its wide use across multiple architectures.

#### 1.3 Requirements

The Pluto 6 was not expected to perform well running an OS, but would serve as a case study for

Heber, as well as an interesting project. The specification for the project was therefore left open, however suggested drivers to write for the board included:

- An IDE driver to access a file system on the Compact Flash card.

- Communication with the PIC micro controller via the I2C bus, allowing access to a real time clock and security logs.

- Communication with the EEPROM via I2C, possibly accessible as a character based device, e.g. / dev/e2rom.

- Reading/writing of the general purpose I/O and lamps, possibly accessible as individual files in / proc.

- Frame buffer driver for the Cremson Graphical Processing Unit (GPU), possibly leading to a driver for the TinyX X server.

- Sound driver, possibly integrated with Advanced Linux Sound Architecture.

## 1.4 Project life cycle

The project life cycle for this project was different to that of regular software development. Because of the amount of fixed variables in the system, i.e. the kernel software architecture and the hardware of the board, the project was split into separate stages. The first stage was to port the kernel to run from RAM, using rapid prototyping methods. Each stage following that was to develop a device driver, the methods and design techniques used in these stages varied from bottom-up to top-down depending on the level of provision in the kernel for that type of device (e.g. the VFD driver was flexible, while the frame buffer and IDE has a very structured kernel subsystem). The only dependency the porting stage had on the later driver stages was for the IDE driver. In order to extend the Kernel to execute in place a disk based file system was required.

## 2 The Pluto 6 board and the current system

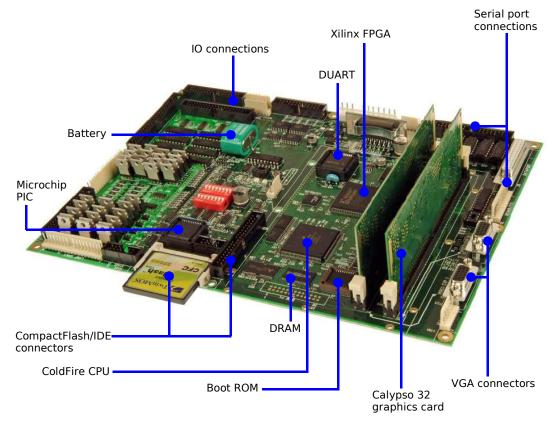

The Pluto 6 is an embedded control board intended for use in coin operated gambling machines. The board has numerous features to target this area:

- The main CPU of the board a Motorola ColdFire, executes the game. It also provides stereo audio using DMA.

- 2Mb of DRAM is used to run the game, also present is 256Kb of battery backed SRAM for frequently accessed or non volatile data.

- IO support a FPGA controls up to 512 multiplexed lamps, each at 8 brightness levels. It also

provides registers to control 64 open drain outputs, and read 32 input switches. The outputs can

be used to drive stepper motors used in the reels of fruit machine cabinets.

- Security the FPGA allows the ColdFire code to be locked to a certain board, preventing piracy.

- A secondary PIC micro controller runs from battery at power down to provide a real time clock, as well as monitoring of security door switches, readings of which are stored in a log. The PIC also reads inputs allowing the percentage payout of a game to be set. Code running on the ColdFire can get data from the PIC over I2C.

- 6 serial ports 2 in the ColdFire, 2 in the FPGA and 2 in a DUART IC. These can all be routed independently by the FPGA to 1 of 4 RS232 ports, 1 RS485, 1 TTL and 2 ccTalk (commonly used by coin acceptors)

- An IDE connection can interface to a hard disc/CompactFlash card (running in true IDE mode) or a CD drive. The Heber boot loader loads the game from disc in S19 format.

- 2 expansion slots allow the board to be fitted with one or two Calypso 32 graphics cards. These are fitted with 32Mb of SDRAM and a Fujitsu Cremson video controller. Standard VGA connectors are provided on the Pluto 6 board. Graphics for video based games can be loaded from an IDE device.

The Pluto 6 is shown here:

Illustration 1 The Pluto 6 gambling machine control board

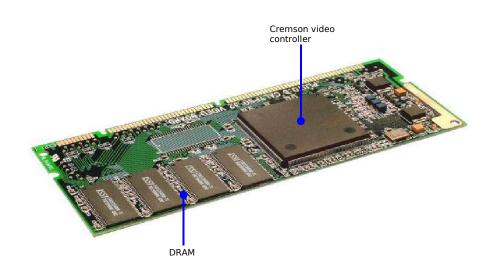

The above image shows two Calypso 32 graphics card inserted. The front side of the Calypso 32 graphics card is shown here:

Illustration 2 The Calypso 32 graphics card

## 2.1 ColdFire CPU background

The CPU used on the Heber Pluto 6 is the Motorola ColdFire 5206e. At the time of writing it is not the most current ColdFire version, newer ones have other peripherals, and the more advanced V4 core. Other ColdFire variants and their features at the time of writing are shown in this table:

| Device         | Dhrys. 2.1<br>MIPS @<br>Max. MHz | Cache<br>SRAM<br>Embedded<br>Flash     | Serial                                    | Timers<br>CS<br>GPIO      | DM<br>A    | DRAM<br>Controller | Operating<br>Frequency<br>(MHz) | Applications                                                          |

|----------------|----------------------------------|----------------------------------------|-------------------------------------------|---------------------------|------------|--------------------|---------------------------------|-----------------------------------------------------------------------|

| 5206e          | 50                               | 4 KB I<br>8 KB<br>-                    | 2 UARTs,<br>1 I2C                         | 2<br>8<br>8               | 2-<br>ch.  | FPM, EDO           | 40, 54                          | Vacuum System<br>Controllers, Printer<br>and LAN Interfaces           |

| 5207/08        | 159                              | 8K I/D<br>16 KB<br>-                   | 3 UARTs,<br>1 opt FEC<br>1 I2C, 1<br>QSPI | 8<br>8<br>Up to 50        | 16-<br>ch. | DDR/SDR<br>SDRAM   | 166                             | Imaging Systems,<br>POS Printers,<br>Networking,<br>Medical Equipment |

| 5211/12/1<br>3 | 76                               | -<br>Up to 32<br>KB<br>Up to 256<br>KB | 3 UARTs,<br>1 I2C, 1<br>QSPI<br>1 opt CAN | Up to 16<br>0<br>Up to 55 | 4-<br>ch.  | -                  | 66, 80                          | Low Power Entry-Level                                                 |

#### The Pluto 6 board and the current system 12

| Device              | Dhrys. 2.1<br>MIPS @<br>Max. MHz | Cache<br>SRAM<br>Embedded<br>Flash | Serial                                                              | Timers<br>CS<br>GPIO                              | DM<br>A   | DRAM<br>Controller        | Operating<br>Frequency<br>(MHz) | Applications                                                    |

|---------------------|----------------------------------|------------------------------------|---------------------------------------------------------------------|---------------------------------------------------|-----------|---------------------------|---------------------------------|-----------------------------------------------------------------|

| 5214/16             | 63                               | 2 KB I<br>64 KB<br>Up to 512<br>KB | 3 UARTs,<br>1 I2C,<br>1 CAN                                         | 8 + 4 DMA<br>7<br>Up to 150                       | 4-<br>ch. | SDR<br>SDRAM              | 66                              | POS, Vending,<br>Industrial Control,<br>Security                |

| 523x                | 150                              | 8 KB I/D<br>64 KB<br>-             | 3 UARTs,<br>2 CANs,<br>1 FEC,<br>QSPI,<br>I2C Opt<br>Encryptio<br>n | Up to 32-<br>ch. eTPU, 4<br>DMA<br>8<br>Up to 113 | 4-<br>ch. | SDR<br>SDRAM              | 80, 100,<br>150                 | Motor Control,<br>Industrial Control                            |

| 5249(L)             | 125                              | 8 KB I<br>96 KB<br>-               | 2 UARTs,<br>2 I 2 C , 4<br>I2 S ,<br>1 QSPI                         | 2<br>4<br>Up to 47                                | 4-<br>ch. | SDR<br>SDRAM              | 140                             | Digital Audio,<br>Industrial Control,<br>Imaging                |

| 5270/71             | 96                               | 8 KB<br>Config.<br>64 KB<br>-      | 3 UARTs,<br>1 I2C, 1<br>FEC,<br>1 QSPI                              | 8<br>8<br>Up to 61                                | 4-<br>ch. | SDR<br>SDRAM              | 100                             | POS, Security,<br>Networking, Gaming,<br>Medical                |

| 5272                | 63                               | 1 KB I<br>4 KB<br>-                | 2 UARTs,<br>1 USB,<br>1 FEC, 1<br>QSPI                              | 4<br>8<br>Up to 32                                | 2-<br>ch. | SDR<br>SDRAM              | 66                              | Imaging Systems,<br>Security, Networking,<br>Telecommunications |

| 5274(L)/<br>5275(L) | 159                              | 16 KB<br>Config.<br>64 KB<br>-     | 3 UARTs,<br>1 I2C,<br>Up to 2<br>FECs,<br>1 USB, 1<br>QSPI          | 8<br>8<br>Up to 61                                | 4-<br>ch. | DDR<br>SDRAM              | 133, 166                        | POS, Security,<br>Networking, Gaming,<br>Medical                |

| 528x                | 76                               | 2 KB I<br>64 KB<br>Up to 512<br>KB | 3 UARTs,<br>1 I 2C ,<br>1 FEC, 1<br>CAN                             | 8 + 4 DMA<br>7<br>Up to 150                       | 4-<br>ch. | SDR<br>SDRAM              | 66, 80                          | Networking,<br>Industrial Control,<br>Security                  |

| 5307                | 75                               | 8 KB U<br>4 KB<br>-                | 2 UARTs,<br>1 I2 C                                                  | 2<br>8<br>16                                      | 4-<br>ch. | SDR<br>SDRAM,<br>FPM, EDO | 66, 90                          | Printer Servers,<br>Barcode Printers,<br>DVB Boxes              |

#### The Pluto 6 board and the current system 13

| Device | Dhrys. 2.1<br>MIPS @<br>Max. MHz | Cache<br>SRAM<br>Embedded<br>Flash | Serial                                                                                   | Timers<br>CS<br>GPIO | DM<br>A    | DRAM<br>Controller        | Operating<br>Frequency<br>(MHz) | Applications                                                                          |

|--------|----------------------------------|------------------------------------|------------------------------------------------------------------------------------------|----------------------|------------|---------------------------|---------------------------------|---------------------------------------------------------------------------------------|

| 532x   | 211                              | 16 КВ<br>32 КВ<br>-                | 3 UARTs,<br>1 I2C, 1<br>FECs,<br>QSPI, USB<br>2.0,<br>opt. CAN,<br>SSI                   | Up to 94             | 16-<br>ch. | DDR/SDR<br>SDRAM          | 240                             | POS, Security/Access,<br>Control, Health Care,<br>Building and Factory<br>Automation  |

| 537x   | 211                              | 16 KB<br>32 KB<br>-                | 3 UARTs,<br>1 I2C,<br>QSPI,<br>SSI                                                       | Up to 62             | 16-<br>ch. | DDR/SDR<br>SDRAM          | 240                             | VoIP, Security/Access,<br>Control, Health Care,<br>Building and Factory<br>Automation |

| 5407   | 316                              | 16 KB I, 8<br>KB D<br>4 KB<br>-    | 1 UART,<br>1 USART,<br>1 I 2C                                                            | 2<br>8<br>16         | 4-<br>ch.  | SDR<br>SDRAM,<br>FPM, EDO | 162, 220                        | Mediaweb Boxes,<br>Digital Video Recorders,<br>Telecom Cards                          |

| 547x   | 410                              | 32 KB I, 32<br>KB D<br>32 KB<br>-  | 4 PSCs,<br>Up to 2<br>FECs,<br>1 I2C, 1<br>PCI,<br>1 DSPI,<br>opt. USB<br>2.0            | 6<br>6<br>Up to 99   | 16-<br>ch. | DDR/SDR<br>SDRAM          | 200, 266                        | POS, Network-<br>Attached Storage,<br>Security/Access Control                         |

| 548x   | 308                              | 32 KB I, 32<br>KB D<br>32 KB<br>-  | 4 PSCs,<br>Up to 2<br>FECs,<br>1 I2C, 1<br>PCI, 1<br>DSPI,<br>opt. USB<br>2.0, 2<br>CANs | 6<br>6<br>Up to 99   | 16-<br>ch. | DDR/SDR<br>SDRAM          | 166, 200                        | Building and<br>Factory Automation,<br>Process Control<br>Equipment                   |

Table 1 Feature comparison of the ColdFire range

See appendix A for further information on the ColdFire and its differences to the 68000.

## 2.2 Further Pluto 6 information

See appendix B for details of the other hardware present on the Pluto 6 board, and how the ColdFire is configured for it.

## 2.3 Current software system

See appendix C for details of the current Heber software architecture.

# 3 uClinux

#### 3.1 Overview

The uClinux kernel was created to support mid range micro controller units which operate at a sufficient speed can address enough memory to run an OS, but do not have a memory management unit (MMU). UClinux is distributed as patches to the main Linux kernel sources, versions are available for releases of the 2.0, 2.4 and 2.6 series kernels. Regular distribution releases are also available, comprising the following:

- the latest pre-patched versions of the 2.0, 2.4 and 2.6 kernel sources

- a much smaller standard C library called uClibc which has almost all the functionality of Glibc,

- a large list of applications modified to use the much smaller library and less capable kernel, including BusyBox, Tinylogin and MicroWindows/Nano-X.

The minimal changes required to port applications to uClinux are explained later in the chapter. The kernel source patches add new architecture trees under the /arch directory, e.g. arm-nommu, blackfin, cris, m68k-nommu, niosnommu. As well as the extra architectures, several drivers for peripherals on more popular boards featuring the MMU-less architectures are added in the /drivers directory. The most notable change in the kernel is in the area of memory management, where the directory /mmnommu is added as a counterpart to the /mm directory in the top level of the source tree.

## 3.2 History

The history of uClinux is shown in the following table:

| Date     | Event                                                                                   |

|----------|-----------------------------------------------------------------------------------------|

| January  | The first system without a MMU to run a Linux kernel port was the Motorola Dragonball   |

| 1998     | MC68328 using a modified 2.0.33 kernel, implemented in a SCADA controller. Kenneth      |

|          | Albanowski and Dr Jeff Dione undertook the work at a company called Rt-Control.         |

| February | The work on uClinux is released publicly under the GPL. The first target platform to be |

| 1998     | shown publicly running the port was a Palm Pilot PDA with a custom boot loader written  |

|          | especially for the project.                                                             |

| Date      | Event                                                                                     |

|-----------|-------------------------------------------------------------------------------------------|

| September | Refinement of the port continued, and uClinux 2.0.38 was released which became the        |

| 1998      | most widely popular version for use in embedded devices. The popularity was               |

|           | increased by Rt-Controls focus on using the kernel to implement actual working            |

|           | embedded devices, rather than other commercial embedded Linux distributions who           |

|           | focused on software only, e.g. porting the kernel and writing toolkits, then handing      |

|           | further development over to device manufacturers.                                         |

| December  | The hardware focus at Rt-Control was re-enforced by the decision to design and            |

| 1998      | manufacture a single board computer (SBC) known as the uCsimm. This board is an           |

|           | inch high, with a standard 30 pin SIMM form factor. It featured a Motorola DragonBall     |

|           | 68EZ328 similar to that used on the original port, and was equipped with 2Mb ROM,         |

|           | 8Mb RAM, Ethernet controller, serial port and I2C. More importantly the uCsimm was        |

|           | specifically designed to run the uClinux OS, and it became popular for numerous           |

|           | applications. The porting of RTLinux kernel patches to uClinux for this board allowed it  |

|           | to be used as a real time device, for example a robotic arm axis controller, which could  |

|           | receive instructions via Ethernet.                                                        |

|           | While Rt-Control were designing their tiny SBC, a company specialising in embedded        |

|           | VPN and Internet appliances called Moreton Bay Ventures were designing the hardware       |

|           | to go into their NetTel line of network routers. For this application they chose Motorola |

|           | ColdFire CPUs which were to run uClinux, a major design win for the platform.             |

| February  | As a result of the design choices at Moreton Bay new ports were added for the Motorola    |

| 1999      | ColdFire 5206 and 5307 architectures. Moreton Bay and Rt-Control worked closely           |

|           | together during this period creating saleable and useful embedded Linux devices. As       |

|           | interest in the ports grew from other device manufacturers and enthusiasts, Rt-Control    |

|           | began distributing CDs containing the patched kernel, a copy of the uClibc library,       |

|           | patched applications and cross compiling tool chains.                                     |

| Date      | Event                                                                                     |

|-----------|-------------------------------------------------------------------------------------------|

| February  | Rt-Control was acquired by a larger embedded Linux company called Lineo. Lineo's          |

| 2000      | main product was an embedded Linux software development kit known as Embeddix,            |

|           | which closely followed the trends of larger Linux systems. During the takeover process    |

|           | the issue of whether to port uClinux to the 2.2 kernel had arisen. Pressure was applied   |

|           | from Lineo, who faced expectations from outside market forces to be providing the         |

|           | latest kernel versions in their products. There was little advantage in using the 2.2     |

|           | kernel in MMU-less devices, whilst requiring large changes. It was found that merging     |

|           | the 2.0.3x uClinux code and Lineos Embeddix Linux 2.2 SDK was overly complex              |

|           | because the SDK required proprietary start up code in the kernels it built. Implementing  |

|           | this code in the uClinux ports would add little value to the functionality of the working |

|           | systems, and involve significant changes to the code. A further unresolved issue was      |

|           | how to include the MMU-less support in the Embeddix SDK. The decision was made to         |

|           | leave uClinux out of Embeddix, as a result development slowed, and 2.0.3x uClinux         |

|           | kernels remained in use for some time.                                                    |

|           | However Lineo did recognise the potential of uClinux, and resisted several outsider       |

|           | attempts to take over the project. Soon after the acquisition the original Rt-Control     |

|           | members were allowed to continue uClinux development.                                     |

|           | The lack of progression to new kernel versions was fortunate for uClinux. The 2.2         |

|           | kernel code was being developed for larger desktop systems with enhanced feature          |

|           | sets, resulting in kernel sizes that were unreasonably large for uClinux based devices.   |

|           | Kernels using 2.0 could be as small as 200Kb (with networking support), whilst 2.2        |

|           | kernels with the same functionality were typically twice as big. Drivers added to the 2.2 |

|           | kernel could be ported to the 2.0 kernel if required, and required reworking anyway to    |

|           | allow for the lack of fork() command, and the mmap() differences in an MMU-less           |

|           | system.                                                                                   |

| March     | Lineo acquired Moreton Bay Ventures. The acquisition enhanced Lineos expertise base,      |

| 2000      | gave them an office in Australia and allowed Rt-Control and Moreton bay to work more      |

|           | closely as they were now owned by the same parent company.                                |

| September | Jeff Dionne and John Drabik announce they have ported uClinux to an FPGA running the      |

| 2000      | Leon SPARC open source core.                                                              |

|           |                                                                                           |

| 2000 u            | The developments in the 2.4 Linux kernel were deemed valuable enough to warrant its use on MMU-less systems, so due to careful preparation - less than a week after the |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | use on MMU-less systems, so due to careful preparation - less than a week after the                                                                                     |

| o                 |                                                                                                                                                                         |

| 1                 | official 2.4 Linux kernel was released, it was followed by the first uClinux version. The                                                                               |

| þ                 | port was done by former members of both Rt-Control and Moreton Bay at Lineo,                                                                                            |

| ir                | ncluding David McCullough and Greg Ungerer. Since then most interest around uClinux                                                                                     |

| h                 | has been on 2.4, but there is still strong interest and support for 2.0 due to its small                                                                                |

| f                 | footprint.                                                                                                                                                              |

| March T           | The uCsimm SBC was superseded by the uCdimm, with a faster Dragonball CPU, SPI,                                                                                         |

| 2001 s            | serial ports and Ethernet in a DIMM form factor. The uCdimm was sold pre-flashed with                                                                                   |

| it                | ts own uClinux port, and marketed by Lineo.                                                                                                                             |

| June 2001 L       | Lineo announced a new uClinux development board based around an ARM7 CPU.                                                                                               |

| December A        | Around this time Lineo decided to divest itself of several non core businesses. The                                                                                     |

| 2001 o            | priginal Rt-Control group were spun-off. By February 2002 the Rt-Control group had                                                                                      |

| fe                | formed a new company called Arcturus Networks and had maintained the rights to                                                                                          |

| U                 | uClinux.                                                                                                                                                                |

| A                 | Also spun out of Lineo at the same time was Moreton Bay, who then became Snapgear.                                                                                      |

| Т                 | These two new companies continued working closely together much as they had done                                                                                        |

| b                 | before, hosting and managing the uClinux project, and using it as the base for saleable                                                                                 |

| n                 | network devices for VPNs, gateways and control systems.                                                                                                                 |

| January A<br>2002 | A port of uClinux 2.0.38 was released for the Hitachi H8300.                                                                                                            |

| February B        | Bernhard Kuhns releases an RTAI port for uClinux on the Motorola ColdFire, providing a                                                                                  |

| 2002 h            | hard real time solution for deeply embedded Linux devices.                                                                                                              |

| March T           | The uCdimm line grew with the addition of a new board, running on a ColdFire 5272                                                                                       |

| 2002 0            | CPU. The product line is now marketed by Arcturus networks.                                                                                                             |

| April 2002 A      | Arcturus Networks officially took on the hosting of the uClinux project.                                                                                                |

| July 2002         | Greg Ungerer of Snapgear releases the first uClinux distribution for download. This                                                                                     |

| с                 | contains patched 2.0 and 2.4 kernels, uC-Libc and uClibc libraries, and patched user                                                                                    |

| þ                 | programs, including Busybox and Microwindows. Prior to this release, only patches                                                                                       |

| v                 | were supplied for download, which then had to be applied to the standard kernel which                                                                                   |

| v                 | was obtained separately.                                                                                                                                                |

| S                 | Snapgear also announce a new website - uCdot, which they would host to announce                                                                                         |

| а                 | advances in uClinux.                                                                                                                                                    |

| May 2003 C        | David McCullough of Snapgear released a uClinux port for the Hitachi H8 architecture.                                                                                   |

| October A         | ADI released a port of uClinux based on kernel 2.4.6 for their own Blackfin DSP                                                                                         |

| 2003 p            | processor.                                                                                                                                                              |

uClinux 19

| Date       | Event                                                                                   |

|------------|-----------------------------------------------------------------------------------------|

| November   | Dr John Williams of the University of Queensland in Brisbane, Australia released a      |

| 2003       | uClinux port for the Microblaze soft core CPU - a 32 bit RISC processor synthesized for |

|            | Xilinx FPGAs.                                                                           |

| December   | The official release of the 2.6 kernel was closely followed by the uClinux version.     |

| 2003       | Uptake of 2.6 was slow due to the larger footprint and need to port the start-up code   |

|            | for each board to the new kernel. 2.4 remained the main kernel series in use on         |

|            | embedded MMU-less devices.                                                              |

| April 2004 | Arcturus Networks released a new board in the uCdimm series based on the Freescale      |

|            | ColdFire 5282.                                                                          |

Table 2 The history of uClinux

Since 2004 support has continued with releases of standard Linux kernels closely followed by uClinux counterparts. Running a Linux kernel on devices of such low specification mentioned above demonstrates the flexibility of the system. During its history uClinux has been ported to many other MMU-less architectures not mentioned above including the ETRAX, ARM7TDMI and other ARM cores, the NEC v850E and the Intel i960. uClinux has rapidly become a popular choice for embedded Linux systems running on MMU-less CPUs, and also MMU enabled systems, with the MMU turned off for extra speed.

The distribution releases now have built in support for a large range of evaluation boards and target platforms. Non-MMU kernels can be readily run on commercial SBCs, evaluation boards, network routers, soft core CPUs running in FPGAs, and are also popular with hobbyists for porting to a range of unintended targets including the Apple iPod and Nintendo Gameboy Advance.

#### 3.3 Differences to the normal kernel

Most differences to the mainline Linux kernel encountered in uClinux stem from the lack of memory management in the hardware of the target architectures. This has effects both in the kernel and for user processes.

## 3.3.1 The role of the Memory management Unit

A MMU has two main purposes:

- To present a virtual address space to user space applications.

- To prevent the Kernel and applications from corrupting each other

#### 3.3.1.1 Virtual memory

Each application is linked to run from the same virtual address (usually 0), which is done because it isn't known at link time what memory address the kernel will load the program into at run time. While running in user mode the CPU translates virtual addresses given to it by the running process to physical ones, which point to the actual memory chips in which the code or data is residing. The MMU in the CPU performs this operation transparently during the fetch execute cycle, and the normal kernel relies on this management in order to hand control of the CPU over to a process which thinks it is located in one contiguous block. In reality the process could be scattered in sections known as page frames, each containing a "page" of memory. The page frame size (typically 4Kb) is determined by the paging unit of the MMU.

For each running process on the system the kernel must set up and maintain a hierarchical page index, allowing each virtual address to be translated into the offset within a specific page. For example, a processes page index on an Intel® x86 comprises a page directory containing entries to multiple page tables, which in turn point to multiple pages. During code execution the running process will use logical addresses which are passed through an x86 specific layer known as the segmentation unit and translated into linear addresses. The linear addresses then are passed to the paging unit and split down into fields. The first field indexes the page directory to get the page table, the second field indexes the page table to get the page, and finally the offset field points into the page to the memory location required. The final result is the physical memory address. The page index does not need to be fully populated, hence making it hierarchical will save memory from being swallowed up by page directories and tables for small processes requiring only limited memory.

With the paging unit in place a page can be located anywhere in actual memory in relation to other pages. The kernel can also move pages from memory into a swap area on a hard disk, providing a full blown virtual memory system. When a process tries to access a swapped out page, an exception occurs. The kernel handles the exception by reading the required page into memory, updating the page table, and continuing the process.

#### 3.3.1.2 Protection

The MMU also stops processes from overwriting each other or worse, the kernel. Should a process try to write outside of the virtual address space it is currently allocated an exception would be flagged, usually causing the kernel to interrupt and kill off the rogue process.

#### 3.3.2 Running an OS without a MMU

Without a MMU, a CPU has no virtual addresses, only physical ones. Without virtual addresses, there is no need for a paging unit, and so the hardware of the CPU has no notion of pages. Therefore in order to allow processes to run without the assistance of an MMU, the uClinux kernel must take the following measures:

All user processes must be linked to absolute addresses. Every memory address given in any assembly instruction must be a valid physical address. Without paging in hardware, processes can't be split up, so each must be located in memory entirely contiguously.

A process may have others residing above and below it in memory and therefore cannot be allowed to increase the amount of memory allocated to itself at run time. On MMU systems the malloc implementation typically calls the brk system call or the sbrk library wrapper. These calls allocate more space at the end of a processes data segment, thereby increasing the processes address space. When the address space is virtual, this isn't a problem, however on uClinux this address space is physical, increasing it would result in overwriting the start of the next process in physical memory. In order to cope with this, uClinux doesn't implement brk or sbrk, but instead collects the free memory of the system into a single pool of addresses. Any applications which call sbrk must be patched. Allocations are made to processes from this pool using a special malloc implementation. The disadvantage of this technique is that rogue processes can take all the available memory in the system. The advantage of the global pool is that it is managed by the kernel. This means the allocation is transparent to any code that calls malloc, unlike other embedded solutions which require extra code in each application. Also, only the amount of memory required is allocated as opposed to a pre-allocated heap scheme, and memory is easily returned to the global pool as soon as it is freed.

Traditional executable formats for user processes (e.g. ELF) are reliant on virtual memory and therefore cannot be linked to and run from absolute physical memory addresses. To overcome this problem uClinux adds support for FLAT binary executables with the loader code in uClinux/fs/binfmt\_flat.c. A FLAT binary consists of the standard text, data and bss sections, but also contains a relocation table created by the elf2flt tool when the flat format binary is created. The relocation table is required because it isn't known at link time where the data and bss sections will be loaded in memory, and all the addresses used must be actual physical addresses. There are two types of relocation table – Global Offset Table and code RELOCS. The GOT is optional, and if included is placed before the data section. The GOT contains a table of offset addresses pointing into the data section at addresses which need to be altered at run time. When loaded these offsets are added to the actual location of the loaded data section to create physical addresses. The table is then used to step through the loaded data and alter all the addresses within it to point to valid addresses. Code RELOCS use a similar principle to GOT, a table of addresses is created by elf2flt and when loaded these addresses point into values in the data section containing pointers, which are then altered to the correct address values.

A useful side effect of the need to relocate the data and bss sections is that it is easy to implement execute in place (XIP), where the code is left in ROM while the data and BSS are copied to RAM thus freeing up memory. However, the relocation tables cannot be used to alter values in the text section of the binary if XIP is to be used, for the following reasons:

- 1. the same copy of the code in the text section will be used by each instance of the running program

- 2. the text section may be in ROM.

In order for user binaries to execute in place there must be support in the elf2flt tool, the kernel FLAT binary loader code, the compiler tool chain which must create position independent code, and the crt0.0 generated by the library.

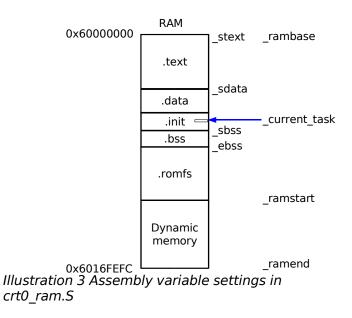

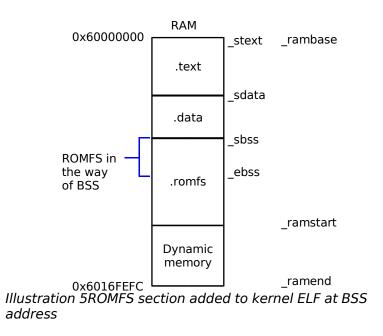

The kernel itself may be XIP enabled, but this isn't dependent on, or specific to uClinux. As long as the text, data, init and bss sections of the kernel image are linked into the appropriate addresses and the kernel entry assembly copies the data section from its Virtual Memory Address (VMA) to its Load Memory Address (LMA), the kernel code can be executed from read only memory (e.g. flash). In order for this to work there must be no variables in the text section of the kernel binary, which rules out certain ports of the kernel, but not the ColdFire port used in this project.

Each process in a multitasking OS requires its own stack. In an MMU system, when a process writes over the top of the stack, an exception is thrown, causing the kernel to step in and allocate more memory, allowing the stack to "grow" as required. As mentioned, a running process on an MMU-less system cannot increase in size dynamically at run time, so a fixed stack size must be set at compile time, and allocated at load time. The FLAT format provides a fixed user process stack size, which is set using the flag passed to the compiler:

```

$ FLTFLAGS = -s <stacksize>

$ export FLTFLAGS

$ make application

```

or changed by calling the flthdr command on the compiled FLAT binary:

flthdr -s <stacksize> executable

The default stack size is 4Kb, although for larger applications such as the busybox binary, a stack size of 20Kb is more suitable. Whilst writing or porting an application for uClinux, developers must be mindful about stack usage. If the limit is exceeded other processes or even the kernel will be

#### corrupted.

Swapping running processes to disk is not feasible to implement, aside from no pages, most uClinux systems don't have hard disks.

uClinux provides an alternative kernel memory allocator. The standard Linux kernel uses a power of 2 memory allocator by default. This groups all the free regions by size in powers of 2 (e.g. Groups for 1, 2, 4, 8, 16 pages etc.) Newly freed regions are split into the nearest power of 2, the remainder is split in the same manner until all the free pages are put into groups. This is a fast method of finding memory regions large enough to satisfy requests. However, every allocation must be a power of 2, which may be wasteful, e.g. A request for 129Kb will allocate 256Kb, wasting 127Kb. This is fine for larger systems, but unacceptable on the memory constrained platforms uClinux is run on. The alternative allocator is still based around pages, even though MMU-less hardware has no notion of them. A large portion of the kernel source including many drivers assumes memory is available in pages, aligned on the appropriate page boundary. Removing all use of pages from the kernel would represent a huge porting effort.

The uClinux kernel memory allocator is called page\_alloc2 or kmalloc2. It uses power of 2 method on a byte basis for allocations up to one page in size, then allocates blocks of memory rounded up to the page size. Page\_alloc2 attempts to avoid memory fragmentation - allocations of two or less pages are made from the start of memory onwards, larger requests are taken from end of memory back. As mentioned uClinux requires large blocks of contiguous memory to load processes, so reducing memory fragmentation is important. RAM constrained systems may find that although there is enough free RAM for a request, there isn't enough in a contiguous block to be able to use it. Defragmenting memory on the fly isn't possible because the contents of an address can't be moved if an active process is using it, the best that can be achieved is to allocate memory wisely before processes are loaded.

uClinux has no fork() system call. On an MMU system, calling fork() would create a new child instance of the process with the same state. The data and bss sections, the heap and the stack of the process are replicated in new areas of memory on the system. The process can continue to use the same addresses to access and change data because the addresses are virtual and will be decoded to unique memory locations by the MMU. If the unmodified fork() were called by a process on uClinux there would be two possibilities:

The child process could share its data with the parent. This will cause problems because the application may be written with the assumption that this is not how fork operates. The two processes could instantly go on to change the data somehow as they run and when they are scheduled in and out of the CPU they could find the data is different to how they left it. This would lead to errors at best and probably corruption of the whole system at worst (especially since

uClinux 24

uClinux has no memory protection)

2. The data of the child process is replicated elsewhere, however all the pointers the process holds to the data are to physical memory addresses and will suddenly become invalid. If the process uses malloc to dynamically allocate more memory at runtime there is no way to account for this in the FLAT relocation tables created at build time by elf2flt.

The simplest solution is to just not have the fork() system call at all. Similar functionality is provided by the vfork() call, it is known by programmers that after this call the parent and child will share the same set of process data. The parent will be suspended until the child either runs a new process by calling exec() (At which point a new process and associated data is created, removing the need to share the parents), or exits. When Linux applications are ported to uClinux, any calls to fork() must be altered to vfork(), allowing programmers to check that no data is modified by the child before it calls exec(). This technique allows multi-tasking in uClinux, after a few adjustments.

Making an application use vfork instead of fork usually falls into the absolutely simple or incredibly difficult category. Generally, if the application does not fork and then exec() almost immediately, it needs to be checked carefully before fork() can be replaced with vfork ().

(McCullough 2004)

As mentioned above there is no brk() system call in the uClinux kernel. In standard C libraries (e.g. Glibc) there is a wrapper for brk() called sbrk() which was originally absent from uClibc, the library that usually accompanies uClinux, until recent later versions which implement sbrk() using the global kernel memory pool rather than expanding the process address space. It is often simpler and more portable however to adjust applications not to use the calls at all.

Certain kernel features are heavily dependent on virtual memory and aren't implemented in uClinux at all, such as tmpfs.

#### 3.3.3 Other differences

Aside from the effects of the lack of memory management hardware, uClinux is typically ran on a variety of unusual and deeply embedded micro controllers. This requires a certain amount of porting work and consideration both in and outside the kernel:

A lot of devices which are used on larger architectures can be put on a SBC (e.g. network interfaces, IDE drives etc.) The drivers for these devices are typically written to operate through certain buses

such as ISA and PCI, resulting in the use low interrupt numbers below 16, and address ranges below 0x3ff which are the consequence of legacy hardware on platforms such as the x86. Most micro controllers running uClinux have no built in support for particular buses and access devices through the local bus interface. Access routines in device drivers to be ported from an ISA platform for example must be altered to use 8/16/32 bit memory mapped IO addresses instead of 16 bit port addresses. Interrupt vector numbers must be selected from the range available on the micro controller rather than one below 16 (typically the vector number is set by the design of the board and cannot be changed, as opposed to the dynamic numbers assigned on the PC).

The mmap() system call is used to map a file into memory. Its usage on uClinux can be controlled so that no extra memory allocation is performed if the file is already in memory within a romfs file system. This efficiency is preferred on the low memory platforms on which uClinux is used, otherwise it must find and allocate a single block of memory large enough, then copy the data from the file into it. In order to avoid memory allocation using mmap certain conditions must be met:

- The romfs file system must be used, because it is the only file system which guarantees that files will be stored contiguously.

- Only read only mappings can be shared, so therefore all memory mapped files must be read only, to avoid memory allocation.

- The file must be either in ROM or RAM, or otherwise contained within the CPUs address space. A file cannot be directly memory mapped if it must first be read from a disc.

## 3.4 Summary

The result of running a Linux kernel on MMU-less hardware aside from the need to adjust applications which use fork(), is a lack of memory protection provided inherently by the MMU for the kernel and processes. The standard kernel uses the MMU as a generic method to protect the kernel from being overwritten by running processes, and protects each process from others. Without a MMU this protection is not provided, allowing programming errors to result in strange erratic behaviour instead of segmentation faults.

The ColdFire on the Pluto 6 provides only very basic memory protection at the device level. Each chip select mask register and DRAM control mask register contains bits in the lower word to allow data or code access for the user or supervisor mode. This could conceivably be used to implement memory protection, by running the kernel from one chip select device or DRAM bank, while allocating memory for the processes and running them from another. However this would not be portable since every board has a different memory configuration, so ensuring the access bits are set correctly for each chip select would make the porting process much more complicate and difficult to maintain. Also many boards only have one bank of RAM and one ROM device, in which case the kernel would have

to store its data on the same memory device as the user processes, so the ColdFire couldn't stop code executing in user mode from overwriting the kernel data. The kernel code could be stored in ROM, but since this can't be written anyway, the protection would be obsolete.

It is perhaps simplest therefore to accept that MMU-less micro controllers such as the ColdFire cannot do adequate memory protection and concentrate on creating portable workarounds for the problem.

## 4 Porting uClinux to the Pluto 6

Before describing the process of porting a uClinux kernel, it is useful to understand the differences at boot between uClinux and the normal kernel.

#### 4.1 Linux kernel boot sequence

When a computer system (anything from a large server to a single board embedded system) is turned on, the method in which the hardware is initialised, the kernel loaded into memory and then executed is totally architecture dependent. Only when the start\_kernel() function is reached (often the earliest part of the kernel to be written in C, rather than assembly) do the many diverse ports of the kernel begin to show common functionality.

The architecture-independent starting point is *start\_kernel* in *init/main.c.* This function is invoked from architecture-specific code, to which it never returns. It is in charge of spinning the wheel and can thus be considered the "mother of all functions," the first breath in the computer's life. Before *start\_kernel*, there was chaos. (Rubini and Corbet, 2001)

An analysis the boot sequence of uClinux compared to the more complex operation required on the x86 PC architecture up until C code is run may be found in appendix D.

#### 4.1.1 After assembly

Once start\_kernel() has been reached, the various ports of uClinux and the standard kernel are all running the same code in linux/init/main.c. However, many of the functions called are unique to each system, residing in files under the arch/ branch in the sources. In particular setup\_arch(), init\_IRQ() and mem\_init(). If a boot loader is used, the method of passing command line options to the kernel varies depending on the boot loader, architecture and even the board for non standardised architectures. Usually, an ASCII string is left in a certain location, such as after the BSS section of the kernel. To deal with this the setup\_arch() function takes a char pointer and points it at the string. setup\_arch() is generally populated with #ifdefs for various machine types containing code which either sets the pointer to the string where it resides, or copies it from a variable created in the boot assembly.

It is during the later stages of the boot in start\_kernel() that mistakes in the earlier assembly can cause problems, making them difficult to track down. On uClinux this is particularly the case with the assembly variables containing pointers to the start and end of RAM, which if wrong can cause

various errors, as was found when porting uClinux to the Pluto 6, described below.

#### 4.2 Design

#### 4.2.1 Kernel version

The 2.4 kernel in the uClinux distribution was chosen for the port, this was because the 2.4 kernel series had support for the most uClinux systems, and was at the time the most used in the uClinux community. This meant the most help would be available if required, many questions were already answered on the uClinux mailing list, and there were example files for other boards to examine.

#### 4.2.2 Kernel location options

There are two main choices of where to place the kernel at run time in an embedded system, RAM or ROM. Which is used is generally determined by the facilities provided by the board. For the Pluto 6 there are several methods to execute code on the ColdFire MCU, and so get an initial uClinux kernel running on the board:

- The ColdFire on the board has 16Kb of internal SRAM, and the Pluto 6 has a 256Kb external SRAM chip. These can be written to by other code, or programmed over BDM, but are both too small to contain a kernel.

- The first code executed by the ColdFire at reset is contained in a 512kb flash EEPROM. This is still

a rather limited size for a uClinux kernel, which has a similar footprint to the standard one. The

EEPROM is a socketed PLCC packaged device, so could in theory be removed and replaced with a

larger one. There are various tools which can program flash devices in-circuit over the BDM cable,

including the open source bdm-load program, so removing the chip and placing it in a programmer

wouldn't be required for each new kernel build. Unfortunately in practice the catalogues of

numerous IC companies didn't contain a pin compatible PLCC packaged EEPROM chip in any size

larger than 512Kb, and this is too small for a kernel and a ROM file system. Although a kernel in

ROM can be debugged, hardware breakpoints can't be set(the instruction at the appropriate

location is replaced by a HALT), so this solution isn't viable for development purposes.

- The Pluto 6 also has a 1.5Mb bank of DRAM, where code is usually run from when the board is

used in gambling machines. This is more than large enough for the games and Heber libraries

which are normally run on the board, but only just large enough for a uClinux kernel. Code can be

downloaded to this memory over BDM and debugged fully. Alternatively the standard Heber boot

loader in the EEPROM can copy an S19 file from a FAT32 partition on the CompactFlash card to

the DRAM and execute it.

Using the DRAM provides the most room for a kernel and the ROMFS file system which is attached to

it by the uClinux build system. Using the Heber boot loader wouldn't provide any of the feedback which the debugger would provide because it is very simple and has no user output, and the Compact flash would need to be removed and mounted on the development host every time a new kernel is to be tested.

So the initial approach chosen to run the kernel on the Pluto 6 was the simplest one – download the kernel to the DRAM over BDM, where it can be debugged.

### 4.3 Implementation

#### 4.3.1 Setting up a development environment

A Linux development host was used because this provides the most support for the build tools and their requirements (e.g. Symbolic links are created for the Busy box target binaries, so they must be built on a file system supporting sym-links). A pre-built cross compiling GCC tool chain was obtained, built to compile for the m68k-elf target. A binary tool chain was downloaded instead of compiling one from scratch for a number of reasons:

- Building a GCC tool chain from scratch is a very complicated procedure requiring certain versions of a number of packages which must be combined to build successfully.

- A pre-built tool chain for the M68K is available which is well tested with the uClinux distribution and is known to compile successfully for all supported variations of the ColdFire micro controller.

At Heber the tool chain used was m68k-coff-gcc, which was the most widely used binary format for Linux kernels before 2.4. However the 2.4 series introduced the init calls mechanism:

The idea of init calls was added in version 2.3.13 and is not available in older kernels; it is designed to avoid hairy #ifdef conditionals all over the initialization code. Every optional kernel feature (device driver or whatever) must be initialized only if configured in the system, so the call to initialization functions used to be surrounded by #ifdef CONFIG\_*FEATURE* and #endif. With init calls, each optional feature declares its own initialization function; the compilation process then places a reference to the function in a special ELF section. At boot time, *do\_initcalls* scans the ELF section to invoke all the relevant initialization functions. (Corbet et al, 2001)

The init sections also allowed GCC specifiers to be used on functions and variables throughout the source, marking them as used for initialisation only. Once the kernel is up and running the memory they occupy can be freed. These sections are defined in linux/include/linux/init.h:

```

#define __init __attribute__ ((__section__ (".text.init")))

#define __initdata __attribute__ ((__section__ (".data.init")))

#else

#define __init

#define __initata

#endif

```

The result of these changes to the kernel is that all ports including uClinux versions had to adopt new tool chains based around a more flexible format than COFF. The most commonly adopted format was ELF which could handle the new init sections. Another advantage of ELF is that it can create the fixed position kernel binary and position independent code user binaries in a single set of tools. COFF required separate tool chains for the kernel and user binaries.

The uClinux distribution version 20041215 (latest at the time) was downloaded and extracted to / usr/src/uClinux-dist/. This distribution contains kernel versions 2.0.39, 2.4.27 and 2.6.9.

At Heber, source level debugging on the Pluto 6 is carried out using a BDM module created by a micro controller development tools specialist called Lauterbach, together with MS windows software called Trace32. The Lauterbach suite is expensive and not supplied with the Pluto 6 development kit. The Pluto 6 DK provides a simpler BDM module made by P&E Micro Systems, with MS Windows software called ICDCFZ. This software allows examination of all ColdFire registers and addressable memory, but isn't as functional as Lauterbachs, since it can't initialise the ColdFire to a working state in a scripted fashion (the boot ROM must be run and then halted before downloading code). ICDCFZ only supports debugging at assembly level only, a proprietary P&E symbol file format is required to debug C source, to create these symbol files requires extra software costs more than the BDM module and ICDCFZ software together.

Since the rest of the tool chain was to run in Linux, debugging in Windows was not preferred. Conveniently, there is a Linux BDM driver and patches to GDB to support debugging 68K/ColdFire targets over the P&E BDM module. Because GDB is a mature, capable debugger, it provides advanced features for the ColdFire target as a matter of course. These features include full C source level debugging as well as assembly stepping, using the well known symbol format in ELF binaries. The other important feature is support for scripting via gdbinit scripts. Once the Module Base Address Register is set, every other register in the ColdFire can be initialised to the correct value – allowing the DRAM to be accessed, and code downloaded. This can all be done in a single script and run every time GDB is started.

The m68k BDM tools package was downloaded, from this a Linux BDM driver module could be built, which operates through device nodes on the host with major number 34, the minor number depends

on the target CPU (68K or ColdFire) and which parallel port the P&E module is connected to. For the ColdFire on LPT1 the device file is:

crw-rw-rw- 1 root root 34, 3 2006-04-09 20:15 /dev/bdmcf0

The device driver operates together with a library which must be installed on the development host. Also provided in the BDM tools package is a small test program called bdm-chk, when run with the device file as an argument this prints the ColdFire type detected and the values of all the CPU registers. See appendix J for the BDM-CHK output.

In practice the BDM device driver wouldn't connect to the target, however the BDM package also provides a BDM network server which when run as root can access the parallel port using the ioperm () system call for compatibility with other Unix versions. The test program and the supplied GDB patches use the library to access the BDM module, the library first tries the Driver, if that fails it will try to access the server on localhost by default. Installing the server and configuring inetd to start it allowed debugging as a normal user without the device driver.

The lack of success with the Linux driver could have been due to peculiarities of the Linux distribution used, however time constraints meant this couldn't be investigated further when a working alternative was available.

In order to use GDB, version 6.0 was downloaded from gnu.org, the patches applied, and GDB built with BDM support. GDB could then be connected to the target with the command:

(gdb) target bdm localhost:/dev/bdmcf0

The register values in the initialisation scripts used at Heber with the Lauterbach suite were referred to in order to create a gdbinit script to bring the Pluto 6 board in to a usable state when GDB is run. See appendix K for the gdbinit script listing.

This allowed the boot ROM to be removed from the board so there would be no doubt what state the hardware was in.

Having set up the tool chain, the uClinux kernels and the Heber source code was set up with the LXR cross referencing tool.

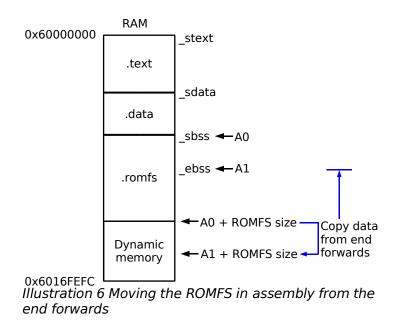

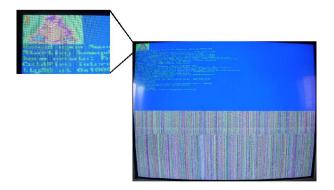

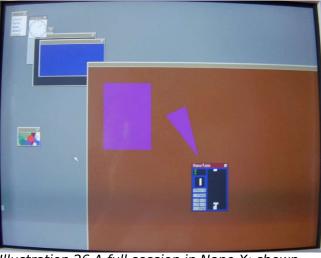

#### 4.3.1.1 Testing the development environment